Rev. 1.0, 02/00, page 462 of 1141

23.1.4

Register Configuration

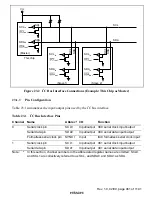

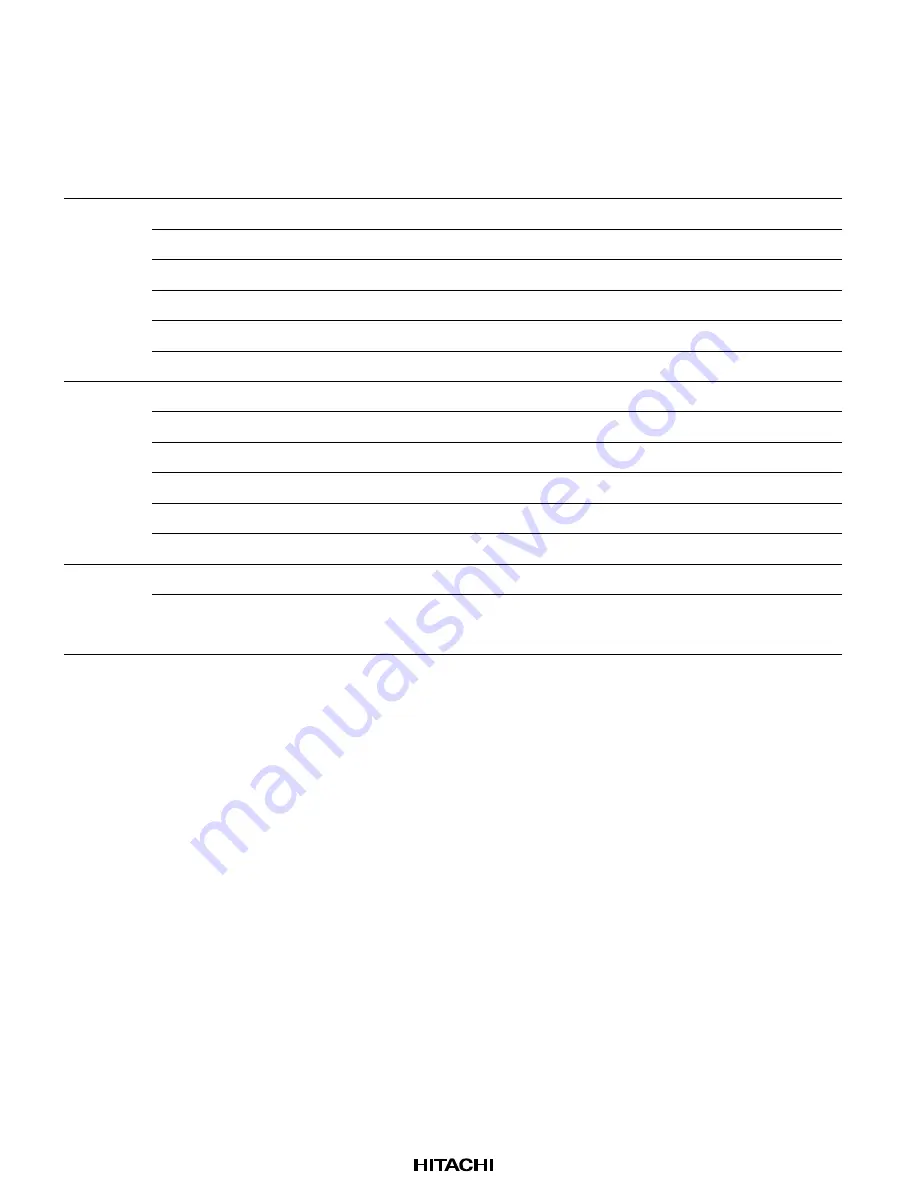

Table 23.2 summarizes the registers of the I

2

C bus interface.

Table 23.2

Register Configuration

Channel

Name

Abbrev.

R/W

Initial Value

Address

*1

0

I

2

C bus control register

ICCR0

R/W

H'01

H'D0E8

I

2

C bus status register

ICSR0

R/W

H'00

H'D0E9

I

2

C bus data register

ICDR0

R/W

H'D0EE*

2

I

2

C bus mode register

ICMR0

R/W

H'00

H'D0EF*

2

Slave address register

SAR0

R/W

H'00

H'D0EF*

2

Second slave address register

SARX0

R/W

H'01

H'D0EE*

2

1

I

2

C bus control register

ICCR1

R/W

H'01

H'D158

I

2

C bus status register

ICSR1

R/W

H'00

H'D159

I

2

C bus data register

ICDR1

R/W

H'D15E*

2

I

2

C bus mode register

ICMR1

R/W

H'00

H'D15F*

2

Slave address register

SAR1

R/W

H'00

H'D15F*

2

Second slave address register

SARX1

R/W

H'01

H'D15E*

2

0 and 1

DDC switch register

DDCSWR

R/W

H'0F

H'D0E5

Module stop control register

MSTPCRH

MSTPCRL

R/W

H'FF

H'FF

H'FFEC

H'FFED

Notes: 1. Lower 16 bits of the address.

2. The registers that can be read from or written to depend on the ICE bit in the I

2

C bus

control register. The slave address registers can be accessed when ICE = 0, and the

I

2

C bus mode registers can be accessed when ICE = 1.