Rev. 1.0, 02/00, page 326 of 1141

Bit 4

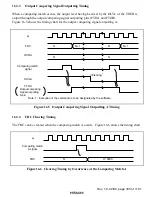

Input Capture Flag D (ICFD): This status flag indicates the fact that the value of the

FRC has been transferred to the ICRD by the input capture signals.

When an input capture signal occurs while the BUFEB of the TCRX is being set to 1, although the

ICFD will be set out, data transference to the ICRD will not be performed.

Therefore, in buffer operation, the ICFD can be used as an external interrupt by setting the ICIDE

bit to 1.

This flag should be cleared by use of the software. Such setting should only be made by use of the

hardware. It is not possible to make this setting using a software.

Bit 4

ICFD

Description

0

[Clearing conditions]

(Initial value)

When 0 is written into the ICFD after reading the ICFD under the setting of ICFD = 1

1

[Setting conditions]

When the input capture signal has occurred

Bit 3

Output Comparing Flag A (OCFA): This status flag indicates the fact that the FRC and

the OCRA have come to a comparing match.

This flag should be cleared by use of the software. Such setting should only be made by use of the

hardware. It is not possible to make this setting using a software.

Bit 3

OCFA

Description

0

[Clearing conditions]

(Initial value)

When 0 is written into the OCFA after reading the OCFA under the setting of OCFA =

1

1

[Setting conditions]

When the FRC and the OCRA have come to the comparing match