Rev. 1.0, 02/00, page 780 of 1141

27.2.9

Noise Detection Level Register (NDETR)

0

0

0

0

0

0

0

0

7

W

NR0

0

W

NR7

6

W

NR6

5

W

NR5

4

W

NR4

3

W

NR3

2

W

NR2

1

W

NR1

Bit :

Initial value :

R/W :

The NDETR is an 8-bit write-only register for specifying the noise detection level. The set value

must be 1/4 of the actual noise detection level. The noise detection window signal is set to 1 at a

falling edge of the OSCH signal, and reset to 0 after the time specified by the HHK period setting

bits has passed. The OSCH signal falls about 5

µ

s after a rising edge of the SEPH signal.

When the noise detection counter value matches the specified noise detection level, the noise

detection interrupt request flag is set to 1. When reset, the NDETR is initialized to H'00. The

NDETR is assigned to the same address as the NDETC.

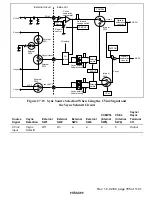

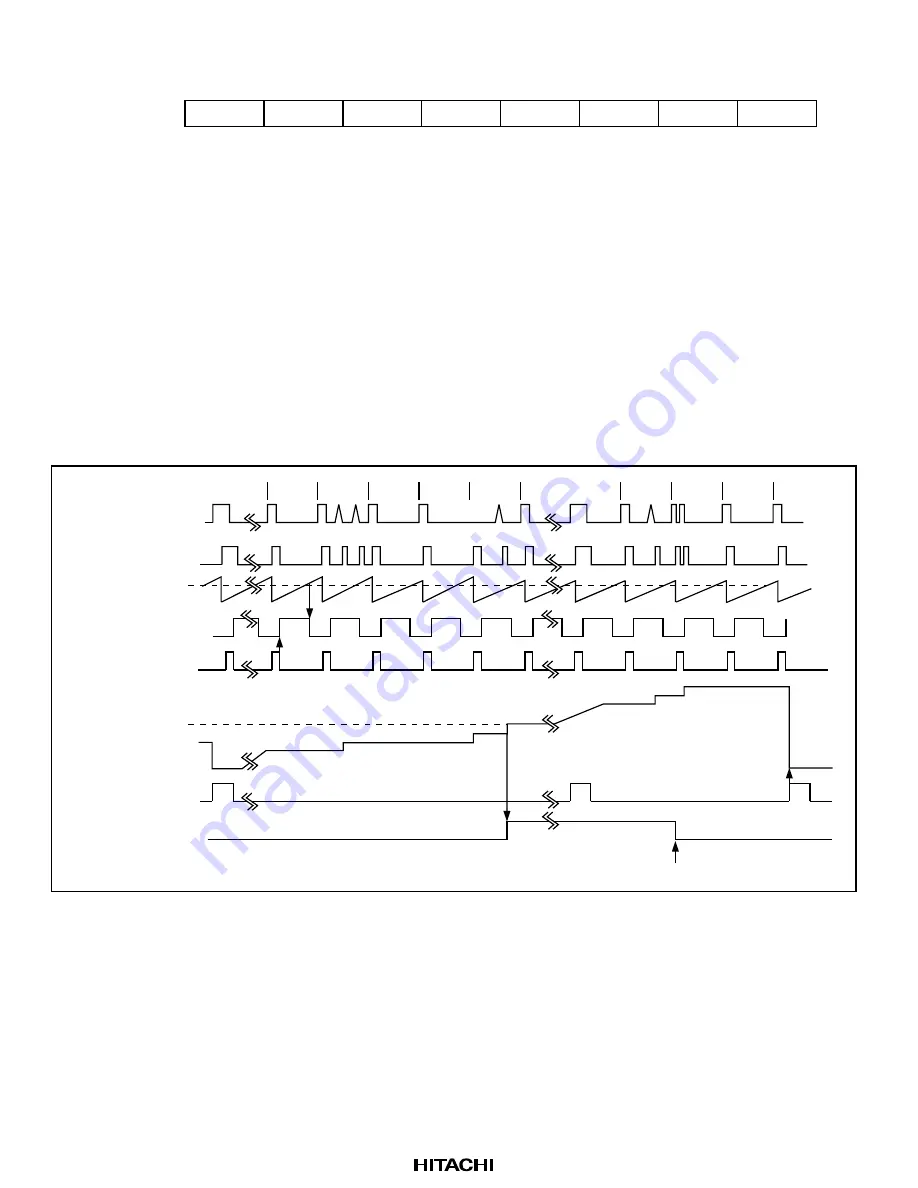

Figure 27.13 shows the timing for noise detection.

Csync

AFCV

NDETC

NDETR

SEPH

OSCH

NDETIF

HM

H complement and

mask counter

Cleared to 0 by CPU

Noise detection window

Noise

Noise

Noise

Noise

Noise counter

cleared

Noise

Comple-

ment

Comple-

ment

Noise

Pulse

lost

Pulse

lost

Figure 27.13 Noise Detection Window Setting and Noise Counting Timing