Rev. 1.0, 02/00, page 701 of 1141

26.13.6

Operation

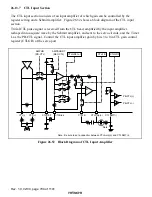

CTL Circuit Operation: As shown in figure 26.49, the CTL discrimination/record circuit is

composed of a 16-bit up/down counter and 12-bit registers (

×

5).

In playback (PB) mode, the 16-bit up/down counter counts on a

φ

s/4 clock when the PB-CTL

pulse is high, and on a

φ

s/5 clock when low. In record or slow mode, this counter increments the

count on a

φ

s/4 clock. In ASM mode, this counter increments the count on a

φ

s/8 clock when the

pulse is high, and on a

φ

s/4 clock when low.

This counter always counts up in record and slow modes.

In playback or slow mode, it is cleared on the rise of PB-CTL signal. In record mode, it is cleared

on the rise of REF30X signal.

φ

s/4

(

φ

s/8)

φ

s/5

(

φ

s/4)

REC-CTL

↓

(L0)

RCDR5

REC-CTL

↓

(S0)

RCDR4

REC-CTL

↓

(L1and ASM)

RCDR3

REC-CTL

↓

(S1)

RCDR2

REC-CTL

↑

Match

detection

Match

detection

Match

detection

Match

detection

Match

detection

RCDR1

12-bit register

UDF:

DOWN

UDF

Upper 12 bits

UP

UP/DOWN counter (16 bits)

Duty

detection

Counter clear signal

REF30X

↑

(REC)

PB-CTL

↑

(PB, ASM)

Up/Down control signal

REC: UP

PB, ASM:

UP when PB-CTL is high

Down when PB-CTL is low

Underflows when PB-CTL

duty is 44% or less

Figure 26.49 CTL Discrimination/Record Circuit

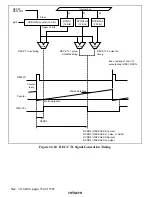

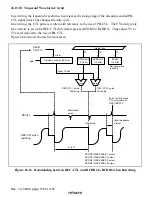

CTL Mode Register (CTLM) Switchover Timing: CTLM is enabled immediately after data is

written to the register. Care must be taken with changes in the operating state.

Capstan phase control is performed by the VD sync REF30X (X-value + tracking value) and PB-

CTL in ASM mode, and by the REF30P or CREF and CFG division signal (DVCFG2) in REC

mode. If CAPREF30 signal to be used for capstan phase control is always generated by XDR, the

value of XDR must be overwritten when switching between PB and REC modes. Figures 26.50

and 26.51 show examples of switch timing of CTLM and XDR.