Rev. 1.0, 02/00, page 888 of 1141

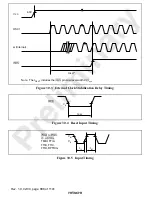

Vcc

OSC1

t

DEXT

*

φ

(Internal)

4.0V

The t

DEXT

includes the

pin Low level width 20 t

cyc

.

Note:

Figure 30.3 External Clock Stabilization Delay Timing

V

IL

t

REL

Figure 30.4 Reset Input Timing

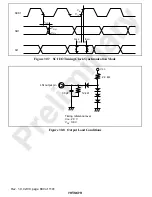

t

IL

t

IH

V

IH

to

,

,

,

TMBI, FTIA,

FTIB, FTIC,

FTID, RPTRIG

V

IL

Figure 30.5 Input Timing