Rev. 1.0, 02/00, page 511 of 1141

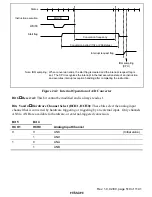

7. Precautions on reading ICDR at the end of master receive mode

When terminating the master receive mode, set TRS bit to 1, and select "write" for ICCR

BBSY = 0 and SCP = 0. This forces to move SDA from low to high level when SCL is at high

level, thereby generating the stop condition.

Now you can read received data from ICDR. If, however, any data is remaining on the buffer,

received data on ICDRS is not transferred to ICDR, thus you won't be able to read the second

byte data.

When it is required to read the second byte data, issue the stop condition from the master

receive state (TRS bit is 0).

Before reading data from ICDR register, make sure that BBSY bit on ICCR register is 0, stop

condition is generated and bus is made free.

If you try to read received data after the stop condition issue instruction (setting ICCR's BBSY

= 0 and SCP = 0 to write) has been executed but before the actual stop condition is generated,

clock may not be appropriately signaled when the next master sending mode is turned on.

Thus, reasonable care is needed for determining when to read the received data.

After the master receive is complete, if you want to re-write IIC control bit (such as clearing MST

bit) for switching the sending/receiving mode or modifying settings, it must be done during period

(a) indicated in figure 23.18 (after making sure ICCR register BBSY bit is cleared to 0).

SDA

SCL

Internal clock

BBSY bit

Bit 0

A

(a)

8

9

Stop condition

Start

condition

Start condition

is issued

Generation of the stop

condition is checked

(BBSY = 0 is set to read)

The stop condition

issue instruction

(BBSY = 0 and SCP = 0

set to write) is executed

Master receive mode

ICDR read

inhibit period

Figure 23.18 Precautions on Reading the Master Receive Data