Rev. 1.0, 02/00, page 1035 of 1141

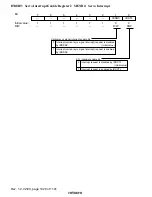

H'D0EF: I

2

C Bus Mode Register ICMR0: I

2

C Bus Interface

7

MLS

0

R/W

6

WAIT

0

R/W

5

CKS2

0

R/W

4

CKS1

0

R/W

3

CKS0

0

R/W

0

BC0

0

R/W

2

BC2

0

R/W

1

BC1

0

R/W

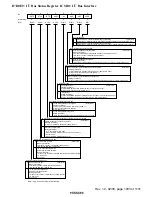

MSB-first/LSB-first select

Note: * See bit 6 in the serial timer control register (STCR)

0 MSB-first

(Initial value)

1 LSB-first

Wait insertion bit

0 Data and acknowledge bits transferred consecutively

(Initial value)

1 Wait inserted between data and acknowledge bits

Transfer clock select bits

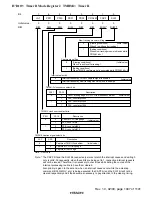

Bit counter

Bit/frame

BC2 BC1 BC0 Clock sync I

2

C bus format

serial format

0 0 0 8 9

(Initial value)

1 1 2

1 0 2 3

1 3 4

0 0 0 4 5

1 5 6

1 0 6 7

1 7 8

IICX* CKS2 CKS1 CKS0 Clock Transfer rate

φ

=8 MHz

φ

=10 MHz

0 0 0 0

φ

/28

286 kHz

357 kHz

1

φ

/40

200 kHz

250 kHz

1 0

φ

/48

167 kHz

208 kHz

1

φ

/64

125 kHz

156 kHz

1 0 0

φ

/80

100 kHz

125 kHz

1

φ

/100

80.0 kHz

100 kHz

1 0

φ

/112

71.4 kHz

89.3 kHz

1

φ

/128

62.5 kHz

78.1 kHz

1 0 0 0

φ

/56

143 kHz

179 kHz

1

φ

/80

100 kHz

125 kHz

1 0

φ

/96

83.3 kHz

104 kHz

1

φ

/128

62.5 kHz

78.1 kHz

1 0 0

φ

/160

50.0 kHz

62.5 kHz

1

φ

/200

40.0 kHz

50.0 kHz

1 0

φ

/224

35.7 kHz

44.6 kHz

1

φ

/256

31.3 kHz

39.1 kHz

Bit

Initial value

R/W

:

:

: