Rev. 1.0, 02/00, page 308 of 1141

15.4

Interrupt Cause

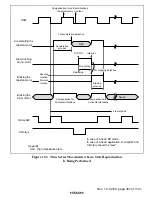

In timer R, bits TMRI1 to TMRI3 of the timer R control/status register cause interrupts. The

following are descriptions of the interrupts.

1. Interrupts caused by the underflowing of the TMRU-1 (TMRI1)

These interrupts will constitute the timing for reloading with the TMRU-1.

2. Interrupts caused by the underflowing of the TMRU-2 or by an end of the acceleration or

braking process (TMRI2)

When interrupts occur at the reload timing of the TMRU-2, clear the AC/BR

(acceleration/braking) bit of the timer R mode register 1 (TMRM1) to 0.

3. Interrupts caused by the capture signals of the TMRU-2 and by ending the slow tracking

mono-multi process (TMRI3)

Since these two interrupt causes are constituting the OR, it becomes necessary to determine

which interrupt cause is occurring using the software.

Respective interrupt causes are being set to the CAPF flag or the SLW flag of the timer R

mode register 2 (TMRM2), have the software determine which.

Since the CAPF flag and the SLW flag will not be cleared automatically, program the software

to clear them. (Writing 0 only is valid for these flags.) Unless these flags are cleared,

detection of the next cause becomes unworkable. Also, if the CP/SLM bit is changed leaving

these flags uncleared as they are, these flags will get cleared.