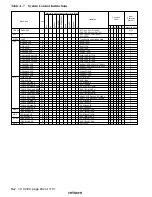

Rev. 1.0, 02/00, page 946 of 1141

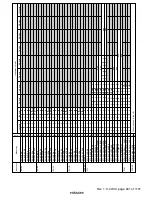

Instruction code:

1st byte

2nd byte

AH

AL

BH

BL

3rd byte

4th byte

CH

CL

DH

DL

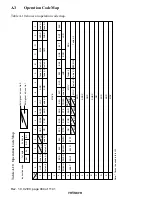

r is the register specification section.

Absolute address is set at aa.

DH highest bit is set to 0.

DH highest bit is set to 1.

Notes:

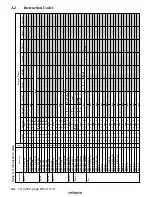

AH AL BH BL CH

CL

01C05

01D05

01F06

7Cr06 *

1

7Cr07 *

1

7Dr06 *

1

7Dr07 *

1

7Eaa6 *

2

7Eaa7 *

2

7Faa6 *

2

7Faa7 *

2

0

MULXS

BSET

BSET

BSET

BSET

1

DIVXS

BNOT

BNOT

BNOT

BNOT

2

MULXS

BCLR

BCLR

BCLR

BCLR

3

DIVXS

BTST

BTST

BTST

BTST

4

OR

5

XOR

6

AND

789

A

B

C

D

E

F

1.

2.

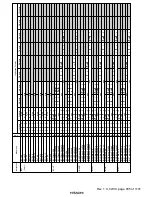

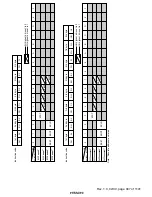

BOR

BIOR

BXOR

BIXOR

BAND

BIAND

BLD

BILD

BST

BIST

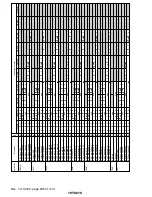

BOR

BIOR

BXOR

BIXOR

BAND

BIAND

BLD

BILD

BST

BIST