Rev. 1.0, 02/00, page 1092 of 1141

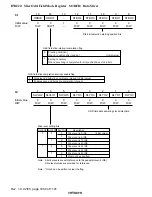

H'FFBA: Timer Mode Register A TMA: Timer A

0

0

1

0

R/W

2

0

R/W

3

0

4

1

5

1

6

0

7

R/W

R/W

R/W

TMAIE

0

R/(W)*

TMAOV

TMA3

TMA2

TMA1

TMA0

Note: * Only 0 can be written to clear the flag.

[Clearing conditions]

(Initial value)

When 0 is written to TMAOV after reading

TMAOV = 1

[Setting conditions]

When TCA overflows

0

1

Timer A overflow flag

Interrupt request by Timer A (TMAI) is disabled (Initial value)

Interrupt request by Timer A (TMAI) is enabled

0

1

Timer A interrupt enable bit

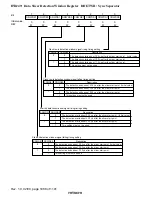

Timer A clock source is PSS (Initial value)

Timer A clock source is PSW

0

1

Clock source, prescaler select bit

PSS,

φ

/16384

(Initial value)

TMA1

TMA0

TMA2

Prescaler frequency division rate (interval timer)

or overflow frequency (time-base)

Operation mode

PSS,

φ

/8192

PSS,

φ

/4096

PSS,

φ

/1024

0

TMA3

PSS,

φ

/512

PSS,

φ

/256

PSS,

φ

/64

PSS,

φ

/16

1 s

Interval timer

mode

Clock time

base mode

0.5 s

0.25 s

0.03125 s

0

1

0

1

1

Clear PSW and TCA to H'00

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Clock select bits

Note:

φ

= f osc

Bit :

Initial value :

R/W :

—

—

—

—