Rev. 1.0, 02/00, page 771 of 1141

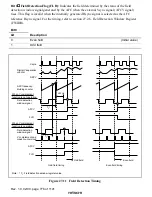

Csync

HVTH

SEPH

Digital H separation

counter

About

3.2

µ

s to 2.0

µ

s

Figure 27.4 HVTH Value and SEPH Generation Timing

When Equalizing Pulses Are Not Detected

The following shows examples of HVTHR settings.

Condition:

(HVTHR – 1)

×

(2/OSC) > 1.6

µ

s or 3.2

µ

s

System clock OSC = 10 MHz

2/OSC = 5 MHz = 0.2

µ

s

Example 1: To detect equalizing pulses

Hsync detection threshold value: 1.6

µ

s

1.6

µ

s / 0.2

µ

s = 8

HVTHR value = H'8 (8)

Example 2: To not detect equalizing pulses

Hsync detection threshold value: 3.2

µ

s

3.2

µ

s / 0.2

µ

s = 16

HVTHR value = H'10 (16)

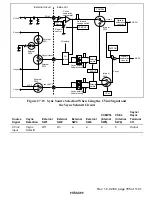

In general, to detect Hsync pulses continuously, set the HVTHR value so that 2.35-

µ

s equalizing

pulses can be detected. However, if an equalizing pulse at an Hsync pulse position is lost in a

weak field, a Hsync-Vsync phase-difference error will occur, and the field will not be detected

correctly. In such a weak field, this error can be prevented by eliminating 2.35-

µ

s equalizing

pulses. Figure 27.5 shows the timing when a phase-difference error occurs.