Rev. 1.0, 02/00, page 329 of 1141

Bit 4

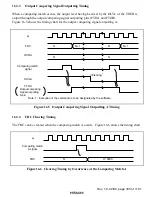

Input Capture Signal Edge Selection D (IEDGD): This bit works to select the rising

edge or falling edge of the input capture signal D (FTID).

Bit 4

IEDGD

Description

0

Captures the falling edge of the input capture signal D

(Initial value)

1

Captures the rising edge of the input capture signal D

Bit 3

Buffer Enabling A (BUFEA): This bit works to select whether or not to use the ICRC as

the buffer register for the ICRA.

Bit 3

BUFEA

Description

0

Not using the ICRC as the buffer register for the ICRA

(Initial value)

1

Using the ICRC as the buffer register for the ICRA

Bit 2

Buffer Enabling B (BUFEB): This bit works to select whether or not to use the ICRD as

the buffer register for the ICRB.

Bit 2

BUFEB

Description

0

Not using the ICRD as the buffer register for the ICRB

(Initial value)

1

Using the ICRD as the buffer register for the ICRB

Bits 1 and 0

Clock Select (CKS1, 0): These bits work to select the inputting clock to the FRC

from among three types of internal clocks and the DVCFG.

The DVCFG is the edge detecting pulse selected by the CFG dividing timer.

Bit 1

Bit 0

CKS1

CKS0

Description

0

0

Internal clock: Counts at

φ

/4

(Initial value)

0

1

Internal clock: Counts at

φ

/16

1

0

Internal clock: Counts at

φ

/64

1

1

DVCFG: The edge detecting pulse selected by the CFG dividing timer