Rev. 1.0, 02/00, page 401 of 1141

22.2

Register Descriptions

22.2.1

Receive Shift Register 1 (RSR1)

7

—

6

—

5

—

4

—

3

—

0

—

2

—

1

—

Bit :

R/W :

RSR1 is a register used to receive serial data.

The SCI sets serial data input from the SI1 pin in RSR1 in the order received, starting with the

LSB (bit 0), and converts it to parallel data. When one byte of data has been received, it is

transferred to RDR automatically.

RSR1 cannot be directly read or written to by the CPU.

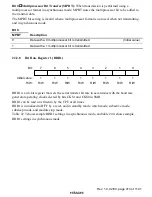

22.2.2

Receive Data Register 1 (RDR1)

7

0

R

6

0

R

5

0

R

4

0

R

3

0

R

0

0

R

2

0

R

1

0

R

Bit :

Initial value :

R/W :

RDR1 is a register that stores received serial data.

When the SCI has received one byte of serial data, it transfers the received serial data from RSR1

to RDR1 where it is stored, and completes the receive operation. After this, RSR1 is receive-

enabled.

Since RSR1 and RDR1 function as a double buffer in this way, continuous receive operations can

be performed.

RDR1 is a read-only register, and cannot be written to by the CPU.

RDR1 is initialized to H'00 by a reset, and in standby mode, watch mode, subactive mode,

subsleep mode, and module stop mode.