Rev. 1.0, 02/00, page 1046 of 1141

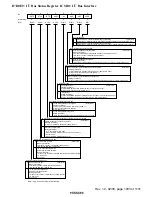

H'D118: Timer R Mode Register 1 TMRM1: Timer R

0

0

1

0

R/W

2

0

R/W

3

0

4

0

R/W

5

0

6

0

7

R/W

R/W

R/W

RLD

R/W

AC/BR

0

R/W

CLR2

RLCK

PS21

PS20

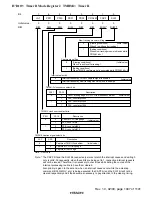

RLD/CAP

CPS

TMRU-2 is not cleard at the time of capture

(Initial value)

TMRU-2 is cleard at the time of capture

0

1

TMRU-2 clear select bit

Deceleration

(Initial value)

Acceleration

0

1

Acceleration/deceleration select bit

TMRU-2 is not used as reload timer

(Initial value)

TMRU-2 is used as reload timer

0

1

Execution/non-execution of reload by TMRU-2

Reload at CFG rising edge

(Initial value)

Reload at TMRU-2 underflow

0

1

TMRU-2 reload timing select bit

0

0

Count at TMRU-1 underflow

(Initial value)

PS20

PS21

1

PSS, count at

φ

/256

0

1

PSS, count at

φ

/128

PSS, count at

φ

/64

1

TMRU-2 clock source select bits

Description

Capture signal at CFG rising edge

(Initial value)

Capture signal at IRQ3 edge

0

1

TMRU-1 capture signal select bit

TMRU-1 functions as reload timer (Initial value)

TMRU-1 functions as capture timer

0

1

TMRU-1 operation mode select bit

Initial value :

Bit

R/W

:

: