Rev. 1.0, 02/00, page 92 of 1141

5.3

Interrupts

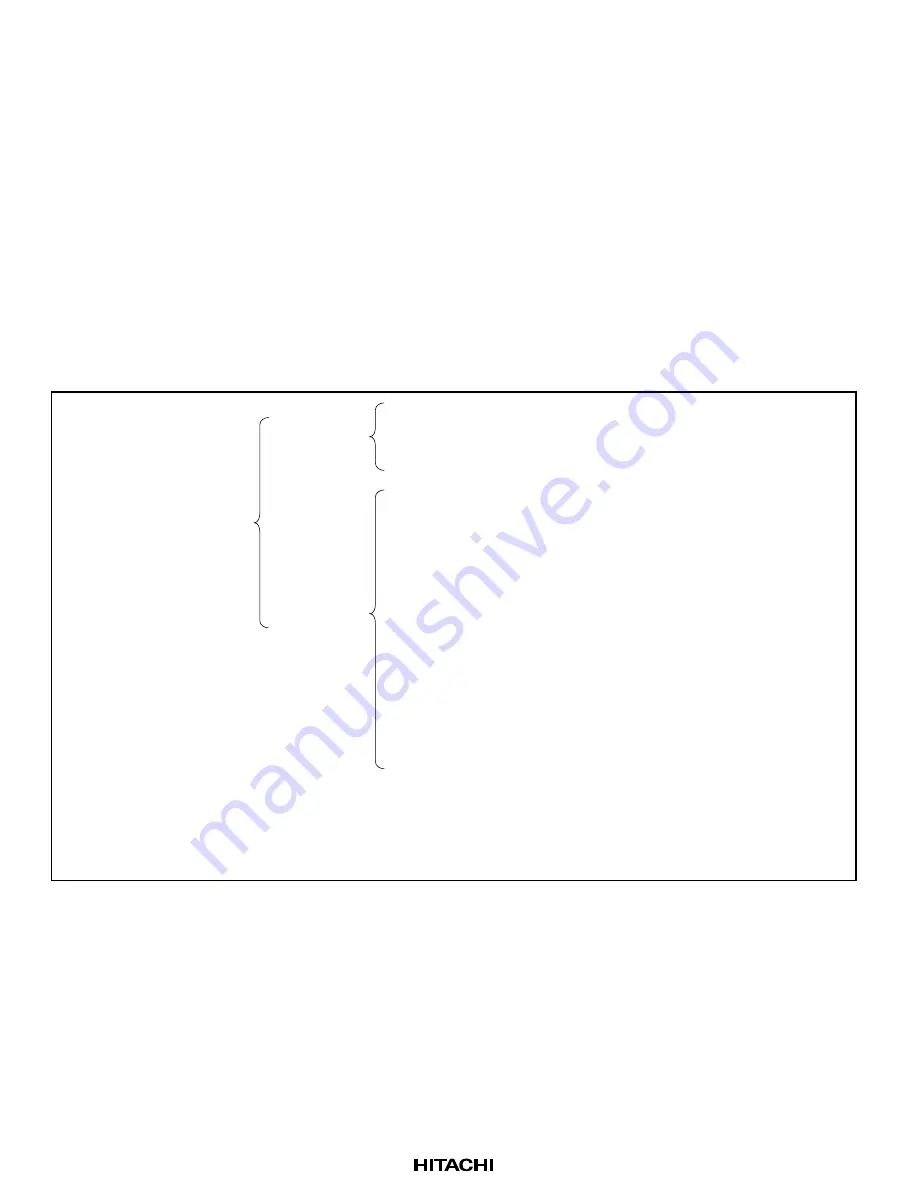

Interrupt exception handling can be requested by six external sources (

,54

8

to

,54

3

) and internal

sources in the on-chip supporting modules. Figure 5.3 shows the interrupt sources and the number

of interrupts of each type.

The on-chip supporting modules that can request interrupts include the watchdog timer (WDT),

prescaler unit (PSU), Timers A, B, J, L, R and X1 (TMR), serial communication interface (SCI),

A/D converter (ADC), I

2

C bus interface (IIC), servo circuits, sync detection, data slicer, OSD,

address trap, etc. Each interrupt source has a separate vector address.

NMI is the highest-priority interrupt. Interrupts are controlled by the interrupt controller. The

interrupt controller has two interrupt control modes and can assign interrupts other than NMI to

either three priority/mask levels to enable multiplexed interrupt control.

For details on interrupts, see section 6, Interrupt Controller.

WDT

*

2

(1)

PSU (1)

TMR (15)

SCI (4)

ADC (1)

IIC (3)

Servo circuits (9)

Synchronized detection (1)

Address trap (3)

Interrupts

Internal

interrupts

External

interrupts

Notes: Numbers in parentheses are the numbers of interrupt sources.

In this LSI, the watchdog timer generates NMIs.

When the watchdog timer is used as an interval timer, it generates an interrupt

request at each counter overflow.

1.

2.

NMI

*

1

(1)

IRQ5 to IRQ0 (6)

Figure 5.3 Interrupt Sources and Number of Interrupts