Rev. 1.0, 02/00, page 994 of 1141

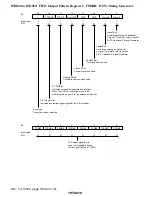

H'D038: Drum Speed Error Detection Control Register

DFVCR: Drum Speed Error Detector

0

0

1

0

(R)/W

*2

2

0

R/W

3

0

4

0

R/W

0

R/(W)

*1

5

6

0

7

DFRFON DF-R/UNR

DPCNT

DFRCS1

DFRCS0

0

R/W

DFCS1

(R)/W

*2

R

R/W

DFCS0

DFOVF

Notes:

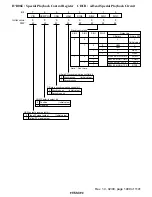

Clock source select bit

DFCS1 DFCS0

0 0

φ

s (Initial value)

1

φ

s/2

1 0

φ

s/4

1

φ

s/8

Counter overflow flag

0 Normal status (Initial value)

1 Counter overflows.

Error data limit function select bit

0 Limit function OFF (Initial value)

1 Limit function ON

Drum lock flag

0 Drum speed system is not locked. (Initial value)

1 Drum speed system is locked.

Drum phase system filter computation auto start bit

0 Filter computation by drum lock detection is not excuted. (Initial value)

1 Filter computation of phase system is executed at the time of

drum lock detection.

Drum lock counter setting bit

DFRCS1 DFRCS0 Description

0 0 Underflow by 1 lock detection (Initial value)

1 Underflow by 2 lock detections

1 0 Underflow by 3 lock detections

1 Underflow by 4 lock detections

Description

Bit :

Initial value :

R/W :

1. Only 0 can be written.

2. When read, counter value is read.