Rev. 1.0, 02/00, page 297 of 1141

15.2.3

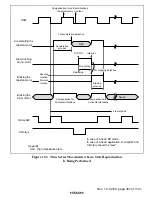

Timer R Control/Status Register (TMRCS)

0

1

1

—

—

—

—

1

2

0

R/(W)*

3

0

4

0

R/(W)*

5

0

6

0

7

R/(W)*

R/W

TMRI1E

R/W

TMRI2E

0

R/W

TMRI3E

TMRI3

TMRI2

TMRI1

Note: * Only 0 can be written to clear the flag.

Bit :

Initial value :

R/W :

The timer R control/status register (TMRCS) works to control the interrupts of timer R.

The TMRCS is an 8-bit read/write register. When reset, the TMRCS is initialized to H'03.

Bit 7

Enabling the TMRI3 Interrupt (TMRI3E): This bit works to permit/prohibit occurrence

of the TMRI3 interrupt when an interrupt cause being selected by the CP/SLM bit of the TMRM2

has occurred, such as occurrences of the TMRU-2 capture signals or when the slow tracking

mono-multi processing ends, and the TMRI3 has been set to 1.

Bit 7

TMRI3E

Description

0

Prohibits occurrences of TMRI3 interrupts

(Initial value)

1

Permits occurrences of TMRI3 interrupts

Bit 6

Enabling the TMRI2 Interrupt (TMRI2E): This bit works to permit/prohibit occurrence

of the TMRI2 interrupt when the TMRI2 has been set to 1 by issuance of the underflow signal of

the TMRU-2 or by ending of the slow tracking mono-multi processing.

Bit 6

TMRI2E

Description

0

Prohibits occurrences of TMRI2 interrupts

(Initial value)

1

Permits occurrences of TMRI2 interrupts