Rev. 1.0, 02/00, page 507 of 1141

End

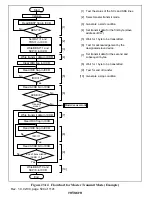

Write transmit data in ICDR

Clear IRIC flag in ICCR

Clear IRIC flag in ICCR

Read ACKB bit in ICSR

Set TRS=0 in ICCR

Read ICDR

Read IRIC flag in ICCR

IRIC=1?

Yes

Yes

No

No

[1]

[4]

[5]

[2]

[3]

Slave transmit mode

End of transmission

(ACKB=1)?

Clear IRIC in ICCR

Set transmit data for the second and

subsequent bytes.

Wait for 1 byte to be transmitted.

Test for end of transfer.

Select slave receive mode.

Dummy read (to release the SCL line).

[1]

[2]

[3]

[4]

[5]

Figure 23.17 Flowchart for Slave Receive Mode (Example)

23.3.10

Initializing Internal Status

The IIC can forcibly initialize the IIC internal status when a dead lock occurs during

communication. Initialization is enabled by (1) setting the CLR3 to CLR0 bits in DDCSWR, or (2)

clearing the ICE bit. For details on CLR3 to CLR0 settings, refer to section 23.2.8, DDC Switch

Register (DDCSWR).

(1) Initialized Status

This function initializes the following:

•

TDRE and RDRF internal flags

•

Transmit/receive sequencer and internal clock counter

•

Internal latches (wait, clock, or data output) which holds the levels output from the SCL and

SDA pins

This function does not initialize the following:

•

Register contents (ICDR, SAR, SARX, ICMR, ICCR, ICSR, DDCSWR, and STCR)