Rev. 1.0, 02/00, page 795 of 1141

Table 27.4

Reference Hsync Signal for AFC

AFC

Reference

Hsync

Signal

Data Slicer

Operation

OSD

Operation

Field

Detection

V Comple-

ment and

Mask

Counter

HCKSEL

HSEL

VCKSL

External

Hsync

signal

Operates/

Stops

Super-

imposed

mode

Operates

Twice the

frequency of

the AFCH

0

0

0

Internally

generated

Hsync

signal

Stops

Text

display

mode

Stops

Twice the

frequency of

the OSCH

0

1

1

External

Hsync

signal

*

Operates

Text

display

mode

Operates

Twice the

frequency of

the AFCH

1

0

0

Note:

*

In this case, the Hsync and Vsync signals must be dedicated separation inputs, with both

signals having equal cycles and pulse widths. The FRQSEL bit in the SEPIMR register

must be cleared to 0.

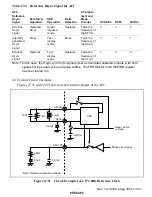

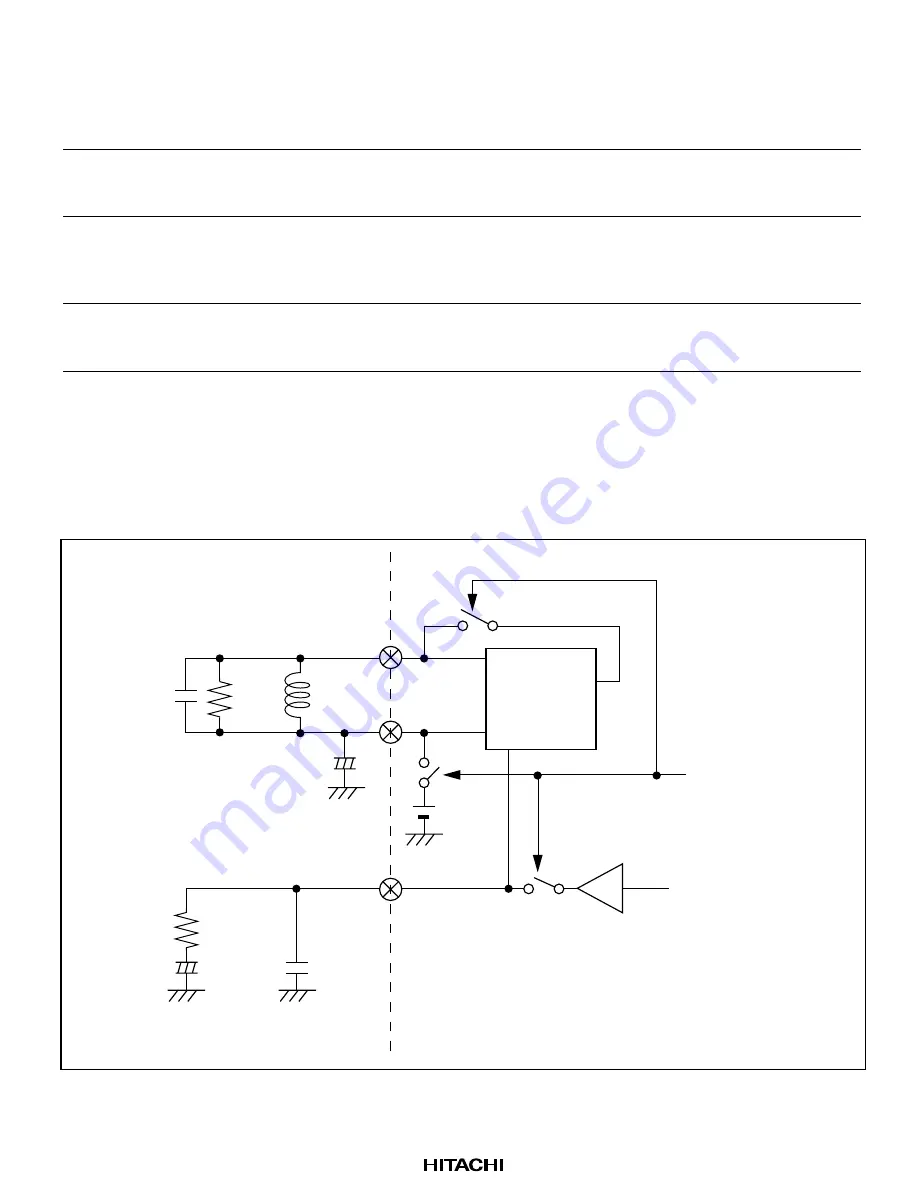

(4) External Circuit Examples

Figures 27.21 and 27.22 show external circuit examples of the AFC.

10pF

AFCosc

AFCpc

AFCLPF

6.8

µ

H

0.01

µ

F

1/2OVcc

VCO

0.01

µ

F

4.7

µ

F

+

+

470

Ω

2.4k

Ω

Note: Reference values are shown.

Phase error signal

Reset, active,

or sleep

Figure 27.21 Circuit Example for a 576

××××

fh Reference Clock