Rev. 1.0, 02/00, page 751 of 1141

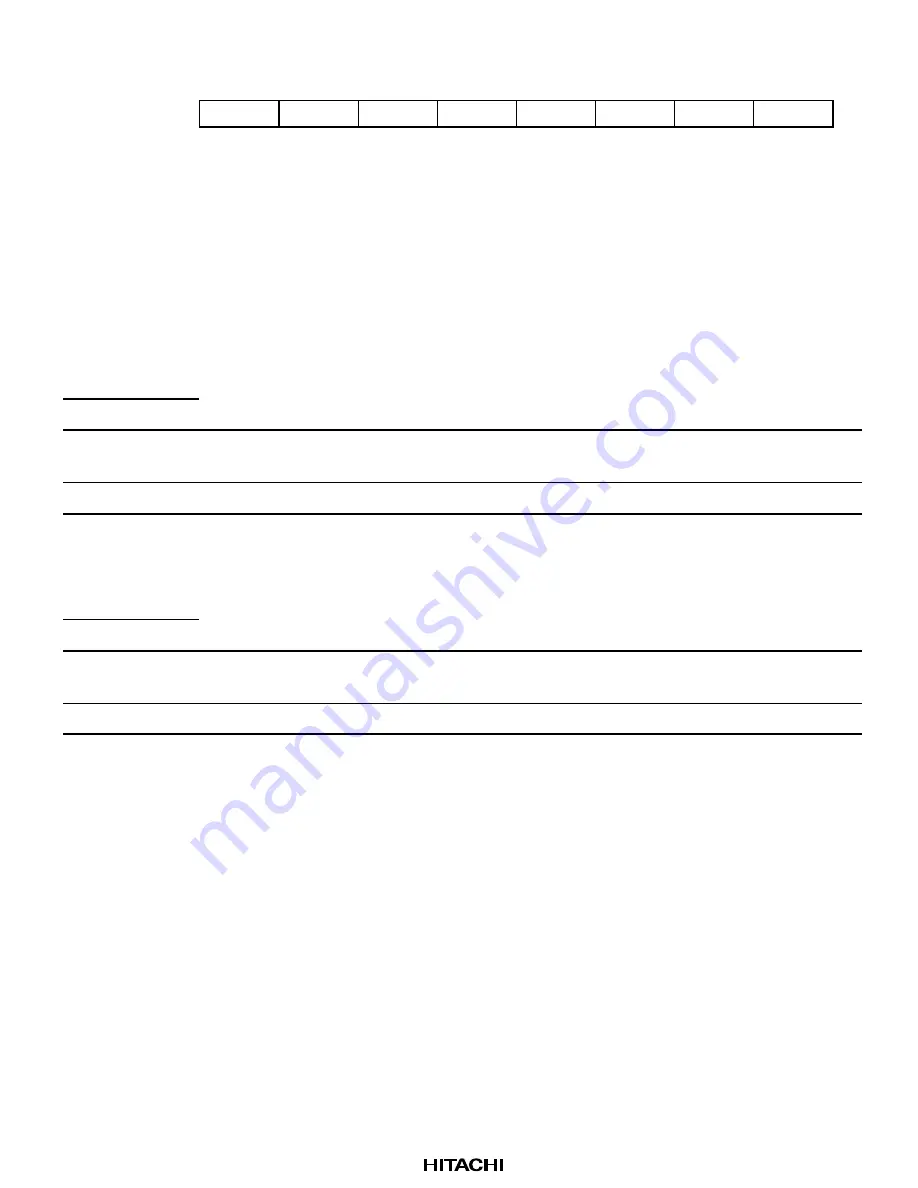

Servo Interrupt Enable Register 2 (SIENR2)

0

0

1

0

R/W

2

3

4

5

6

1

7

—

—

—

—

—

—

—

—

—

—

—

—

R/W

IESNC

IECTL

1

1

1

1

1

Bit :

Initial value :

R/W :

SIENR2 is an 8-bit read/write register that enables or disables interrupts in the servo section. It is

initialized to H'FC by a reset, stand-by or module stop.

Bits 7 to 2

Reserved: Cannot be modified and are always read as 1.

Bit 1

Vertical Sync Signal Interrupt Enable Bit (IESNC)

Bit 1

IESNC

Description

0

Disables the request of the interrupt (interrupt to the vertical sync signal) by

IRRSNC

(Initial value)

1

Enables the request of the interrupt by IRRSNC

Bit 0

CTL Interrupt Enable Bit (IECTL)

Bit 0

IECTL

Description

0

Disables the request of the interrupt by IRRCTL

(Initial value)

1

Enables the request of the interrupt by IRRCTL