Rev. 1.0, 02/00, page 692 of 1141

REC-CTL Duty Data Register 1 (RCDR1)

13

14

15

1

0

3

2

5

4

7

6

9

8

11

10

CMT11

W

12

1

1

1

1

—

—

—

—

—

—

—

—

0

CMT10

W

0

CMT13

W

0

CMT12

W

0

CMT15

W

0

CMT14

W

0

CMT17

W

0

CMT16

W

0

CMT19

W

0

CMT18

W

0

CMT1B

W

0

CMT1A

W

0

Bit :

Initial value :

R/W :

RCDR1 is a 12-bit write-only register that sets the REC-CTL rising timing. This setting is valid

only for recording and rewriting, and is not used in detection.

Only a word access is valid. If a byte access is attempted, correct operation is not guaranteed. If a

read is attempted, an undetermined value is read out. Bits 15 to 12 are reserved and are not

affected by write access.

RCDR1 is initialized to H'F000 by a reset, and in standby mode, module stop mode and CTL stop

mode.

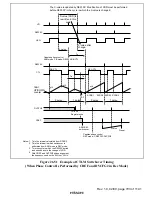

The value to set in RCDR1 can be calculated from the transition timing T1 and the servo clock

frequency

φ

s by the equation given below. See figure 26.60, REC-CTL Signal Generation

Timing. Any transition timing can be set. The timing should be selected with attention to

playback tracking compensation and the latch timing for phase control.

RCDR1 = T1

×

φ

s/64

φ

s is the servo clock frequency (= f

OSC

/2) in Hz, and T1 is the set timing (s).

Note:

0 cannot be set to RCDR1. Set a value 1 or above.