Rev. 1.0, 02/00, page 997 of 1141

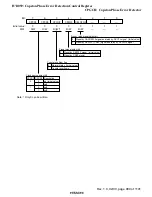

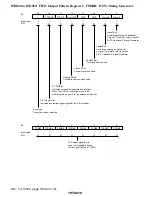

H'D052 to H'D053: CFG Speed Error Data Register

CFER: Capstan Speed Error Detector

0

*

R/W

13

0

*

R/W

14

0

*

R/W

15

1

0

3

2

5

4

7

0

*

R/W

6

0

*

R/W

9

0

*

R/W

8

0

*

R/W

11

0

*

R/W

10

0

*

R/W

0

*

R/W

*

R/W

*

R/W

*

R/W

*

R/W

*

R/W

*

R/W

12

0

0

0

0

0

0

CFER15 CFER14 CFER13 CFER12 CFER11 CFER10 CFER9 CFER8 CFER7 CFER6 CFER5 CFER4 CFER3 CFER2 CFER1 CFER0

Bit

Initial value

R/W

:

:

:

Note: * Only the detected error data can be read.

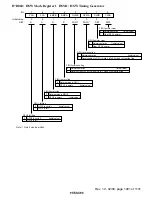

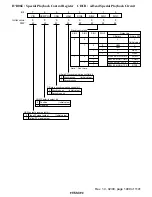

H'D054 to H'D055: CFG Lock Upper Data Register

CFRUDR: Capstan Speed Error Detector

1

W

13

1

W

14

0

W

15

1

0

3

2

5

4

7

1

W

6

1

W

9

1

W

8

1

W

11

1

W

10

1

W

1

W

W

W

W

W

W

W

12

1

1

1

1

1

1

CFRUDR15 CFRUDR14 CFRUDR13 CFRUDR12 CFRUDR11 CFRUDR10 CFRUDR9 CFRUDR8 CFRUDR7 CFRUDR6 CFRUDR5 CFRUDR4 CFRUDR3 CFRUDR2 CFRUDR1 CFRUDR0

Bit

Initial value

R/W

:

:

:

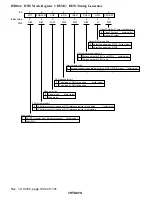

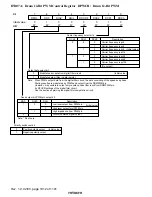

H'D056 to H'D057: CFG Lock Lower Data Register

CFRLDR: Capstan Speed Error Detector

0

W

13

0

W

14

1

W

15

1

0

3

2

5

4

7

0

W

6

0

W

9

0

W

8

0

W

11

0

W

10

0

W

0

W

W

W

W

W

W

W

12

0

0

0

0

0

0

CFRLDR15 CFRLDR14 CFRLDR13 CFRLDR12 CFRLDR11 CFRLDR10 CFRLDR9 CFRLDR8 CFRLDR7 CFRLDR6 CFRLDR5 CFRLDR4 CFRLDR3 CFRLDR2

CFRLDR1 CFRLDR0

Bit

Initial value

R/W

:

:

: