Rev. 1.0, 02/00, page 721 of 1141

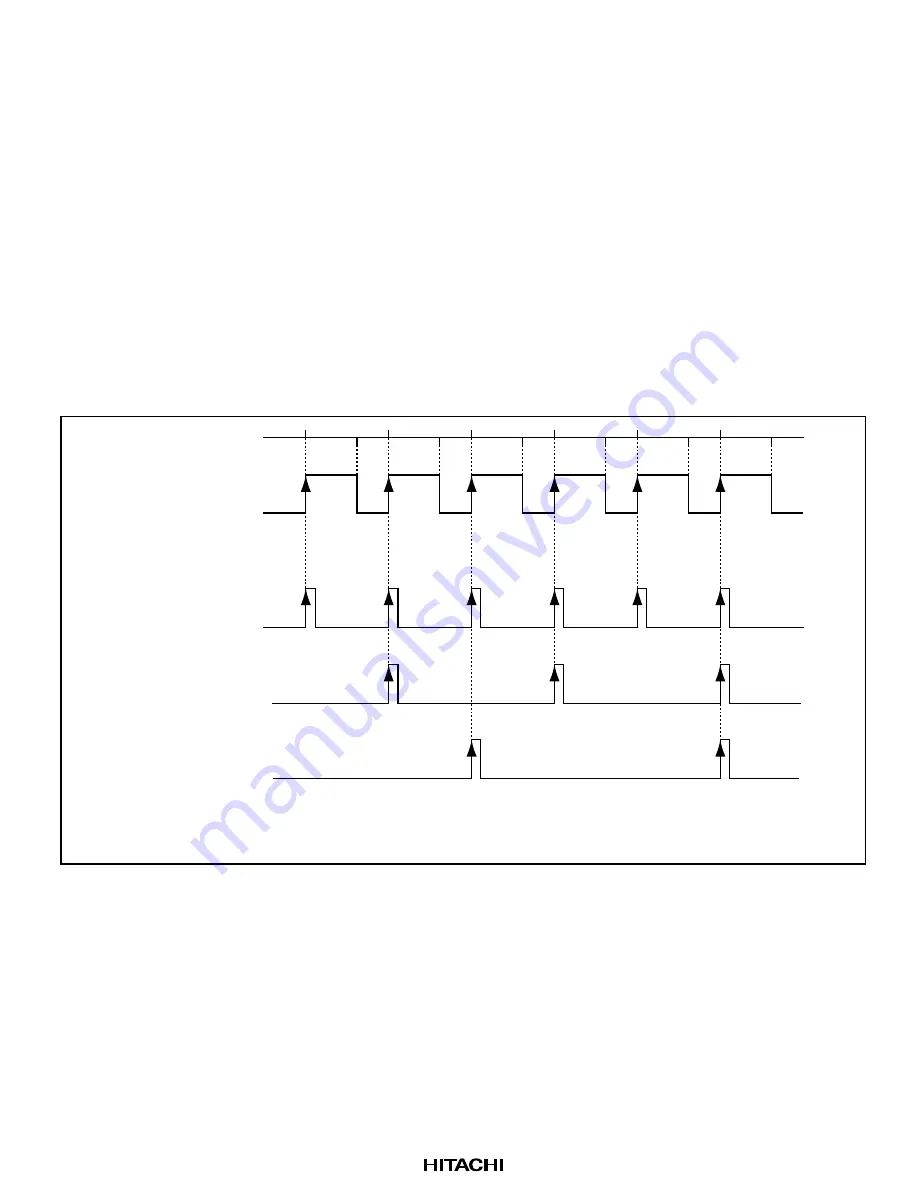

Operation: During playback, control pulses recorded on the tape are picked up by the control

head and input to the CTL pin. The control pulse signal is amplified by a Schmitt amplifier,

reshaped, then input to the CTL frequency divider as the PB-CTL signal.

This circuit is employed when the control pulse (PB-CTL signal) is used for phase control of the

capstan motor. The divided signal is sent as the DVCTL signal to the capstan phase system in the

servo circuits and timer R.

The CTL frequency divider is an 8-bit reload timer consisting of a reload register and a down-

counter. Frequency division is obtained by setting frequency-division data in bits 7 to 0 in the

CTL frequency division register (CTLR), which is the reload register. When a frequency division

value is written in this reload register, it is also written into the down-counter. The down-counter

is decremented on rising edges of the PB-CTL signal.

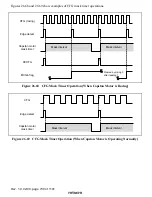

Figure 26.64 shows examples of the PB-CTL and DVCTL waveforms.

CTL input signal

CTLR: CTL frequency division register

PB-CTL or external

sync signal

CTLR=00

CTLR=01

CTLR=02

Figure 26.64 CTL Frequency Division Waveforms