Rev. 1.0, 02/00, page 78 of 1141

4.3

Medium-Speed Mode

When the SCK1 and SCK0 bits in SBYCR are set to 1 in high-speed mode, the operating mode

changes to medium-speed mode at the end of the bus cycle. In medium-speed mode, the CPU

operates on the operating clock (

φ

16,

φ

32 or

φ

64) specified by the SCK1 and SCK0 bits. The on-

chip supporting modules other than the CPU always operate on the high-speed clock (

φ

).

In medium-speed mode, a bus access is executed in the specified number of states with respect to

the bus master operating clock. For example, if

φ

16 is selected as the operating clock, on-chip

memory is accessed in 16 states, and internal I/O registers in 32 states.

Medium-speed mode is cleared by clearing the both bits SCK1 and SCK0 to 0. A transition is

made to high-speed mode and medium-speed mode is cleared at the end of the current bus cycle.

If a SLEEP instruction is executed when the SSBY bit in SBYCR and the LSON bit in LPWRCR

are cleared to 0, a transition is made to sleep mode. When sleep mode is cleared by an interrupt,

medium-speed mode is restored.

If a SLEEP instruction is executed when the SSBY bit in SBYCR is set to 1, and the LSON bit in

LPWRCR and the TMA3 bit in TMA (Timer A) are both cleared to 0, a transition is made to

software standby mode. When standby mode is cleared by an external interrupt, medium-speed

mode is restored.

When the

5(6

pin is driven low, a transition is made to the reset state, and medium-speed mode is

cleared. The same applies in the case of a reset caused by overflow of the watchdog timer.

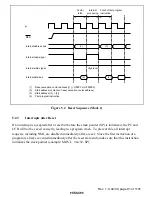

Figure 4.2 shows the timing for transition to and clearance of medium-speed mode.

Medium-speed mode

Internal

φ

,

supporting module clock

CPU clock

Internal address bus

Internal write signal

SBYCR

SBYCR

Figure 4.2 Medium-Speed Mode Transition and Clearance Timing