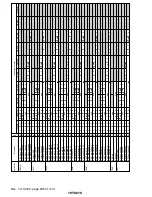

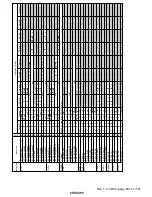

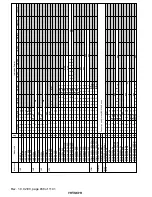

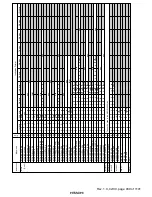

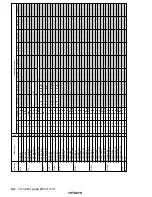

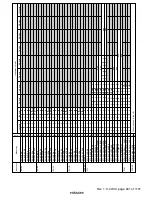

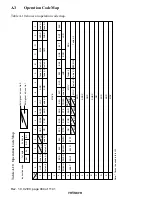

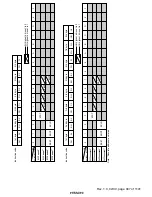

Rev. 1.0, 02/00, page 932 of 1141

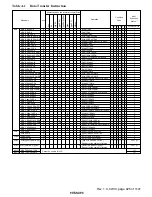

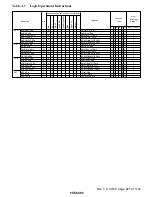

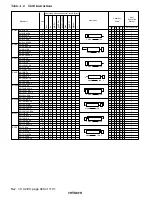

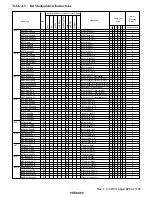

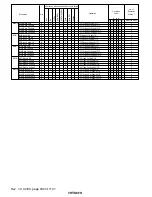

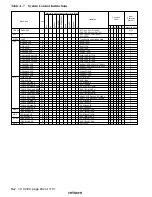

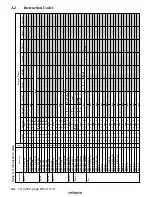

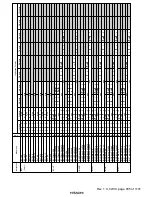

Table A.7

System Control Instructions

TRAPA #x:2

RTE

SLEEP

LDC #xx:8,CCR

LDC #xx:8,EXR

LDC Rs,CCR

LDC Rs,EXR

LDC @ERs,CCR

LDC @ERs,EXR

LDC @(d:16,ERs),CCR

LDC @(d:16,ERs),EXR

LDC @(d:32,ERs),CCR

LDC @(d:32,ERs),EXR

LDC @ERs+,CCR

LDC @ERs+,EXR

LDC @aa:16,CCR

LDC @aa:16,EXR

LDC @aa:32,CCR

LDC @aa:32,EXR

STC.B CCR,Rd

STC.B EXR,Rd

STC.W CCR,@ERd

STC.W EXR,@ERd

STC.W CCR,@(d:16,ERd)

STC.W EXR,@(d:16,ERd)

STC.W CCR,@(d:32,ERd)

STC.W EXR,@(d:32,ERd)

STC.W CCR,@-ERd

STC.W EXR,@-ERd

STC.W CCR,@aa:16

STC.W EXR,@aa:16

STC.W CCR,@aa:32

STC.W EXR,@aa:32

ANDC #xx:8,CCR

ANDC #xx:8,EXR

ORC #xx:8,CCR

ORC #xx:8,EXR

XORC #xx:8,CCR

XORC #xx:8,EXR

NOP

—

—

—

B

B

B

B

W

W

W

W

W

W

W

W

W

W

W

W

B

B

W

W

W

W

W

W

W

W

W

W

W

W

B

B

B

B

B

B

—

TRAPA

RTE

SLEEP

LDC

STC

ANDC

ORC

XORC

NOP

Mnemonic

Size

#xx

Rn

@ERn

@(d,ERn)

@-ERn/@ERn+

@aa

@(d,PC)

@@aa

—

PC

→

@-SP,CCR

→

@-SP,

EXR

→

@-SP,<Vector>

→

PC

EXR

←

@SP+,CCR

←

@SP+,

PC

←

@SP+

Transition to power-down state

#xx:8

→

CCR

#xx:8

→

EXR

Rs8

→

CCR

Rs8

→

EXR

@ERs

→

CCR

@ERs

→

EXR

@(d:16,ERs)

→

CCR

@(d:16,ERs)

→

EXR

@(d:32,ERs)

→

CCR

@(d:32,ERs)

→

EXR

@ERs

→

CCR,ERs32+2

→

ERs32

@ERs

→

EXR,ERs32+2

→

ERs32

@aa:16

→

CCR

@aa:16

→

EXR

@aa:32

→

CCR

@aa:32

→

EXR

CCR

→

Rd8

EXR

→

Rd8

CCR

→

@ERd

EXR

→

@ERd

CCR

→

@(d:16,ERd)

EXR

→

@(d:16,ERd)

CCR

→

@(d:32,ERd)

EXR

→

@(d:32,ERd)

ERd32-2

→

ERd32,CCR

→

@ERd

ERd32-2

→

ERd32,EXR

→

@ERd

CCR

→

@aa:16

EXR

→

@aa:16

CCR

→

@aa:32

EXR

→

@aa:32

CCR

∧

#xx:8

→

CCR

EXR

∧

#xx:8

→

EXR

CCR

∨

#xx:8

→

CCR

EXR

∨

#xx:8

→

EXR

CCR

⊕

#xx:8

→

CCR

EXR

⊕

#xx:8

→

EXR

PC

←

PC+2

Operation

I

H N Z V C

Advanced Mode

2

4

2

4

2

4

2

4

2

2

2

2

4

4

4

4

6

6

10

10

6

6

10

10

4

4

4

4

6

6

8

8

6

6

8

8

2

5 [9]

2

1

2

1

1

3

3

4

4

6

6

4

4

4

4

5

5

1

1

3

3

4

4

6

6

4

4

4

4

5

5

1

2

1

2

1

2

1

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

8 [9]

Condition

Code

Addressing Mode and Instruction Length (Bytes)

No of

Execution

States

*1