Rev. 1.0, 02/00, page 1112 of 1141

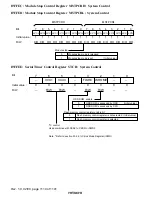

H'FFF2: IRQ Status Register IRQR: Interrupt Controller

0

0

1

0

R/(W)*

2

0

R/(W)*

3

0

4

0

R/(W)*

5

0

0

7

R/(W)*

R/(W)*

R/(W)*

IRQ5F

IRQ4F

IRQ3F

IRQ2F

IRQ1F

IRQ0F

0

6

Note: * Only 0 can be written to clear the flag.

IRQ5 to IRQ0 flag

[Clearing conditions]

Cleared by reading IRQnF set to 1, then writing 0 in IRQnF

When IRQn interrupt exception handling is executed

[Setting conditions]

(1) When a falling edge occurs in IRQn input while falling edge detection is set (IRQnEG = 0)

(2) When a rising edge occurs in IRQn input while rising edge detection is set (IRQnEG = 0)

(3) When a falling or rising edge occurs in IRQ0 input while both-edge detection is set (IRQ0EG1 = 1)

0

1

(n = 5 to 0)

Bit

Initial value

R/W

:

:

:

(Initial value)

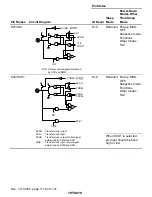

H'FFF3: Interrupt Control Register A ICRA: Interrupt Controller

H'FFF4: Interrupt Control Register B ICRB: Interrupt Controller

H'FFF5: Interrupt Control Register C ICRC: Interrupt Controller

H'FFF6: Interrupt Control Register D ICRD: Interrupt Controller

0

0

1

0

R/W

2

0

R/W

3

0

4

0

R/W

0

R/W

5

0

7

ICR4

ICR3

ICR2

ICR1

ICR0

0

R/W

ICR7

R/W

R/W

R/W

ICR6

ICR5

6

Interrupt control level

Corresponding interrupt source is control level 0 (non-priority)

(Initial value)

Corresponding interrupt source is control level 1 (priority)

0

1

(n = 7 to 0)

Bit

Initial value

R/W

:

:

: