Rev. 1.0, 02/00, page 568 of 1141

φ

s/2

φ

s/4

W

W

CREF

DVCFG2

PB(ASM)

↓

REC

Match

Clear

Counter clear

Toggle

Edge

detection

CRD

W

RCS

Reference period register 2 (16 bits)

Reference period buffer 2 (16 bits)

Comparator (16 bits)

Counter (16 bits)

Internal bus

S

R

Q

Dummy read

φ

s = fosc/2

↑

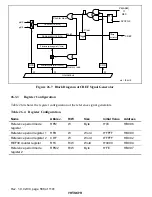

Figure 26.7 Block Diagram of CREF Signal Generator

26.3.3

Register Configuration

Table 26.4 shows the register configuration of the reference signal generators.

Table 26.4

Register Configuration

Name

Abbrev.

R/W

Size

Initial Value

Address

Reference period mode

register

RFM

W

Byte

H'00

H'D096

Reference period register 1

RFD

W

Word

H'FFFF

H'D090

Reference period register 2

CRF

W

Word

H'FFFF

H'D092

REF30 counter register

RFC

R/W

Word

H'0000

H'D094

Reference period mode

register 2

RFM2

R/W

Byte

H'FE

H'D097