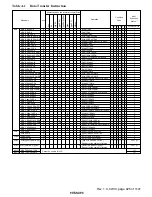

Rev. 1.0, 02/00, page 909 of 1141

Values

Item

Symbol

Applicable

Pins

Test

Conditions

Min

Typ

Max

Unit

Figure

5(6

pin low level

width

t

REL

5(6

Vcc = 2.7 V to

5.5 V

20

t

cyc

Figure

30.13

Input pin high level

width

t

IH

,54

3

to

,54

8

,

,&

,

$'75*

,

TMBI, FTIA,

FTIB, FTIC,

FTID,

RPTRIG

Vcc = 2.7 V to

5.5 V

2

t

cyc

t

subcyc

Input pin low level

width

t

IL

,54

3

to

,54

8

,

,&

,

$'75*

,

TMBI, FTIA,

FTIB, FTIC,

FTID,

RPTRIG

Vcc = 2.7 V to

5.5 V

2

t

cyc

t

subcyc

Figure

30.14

t

cyc

t

CPH

V

IL

V

IH

OSC1

t

CPL

t

CPf

t

CPr

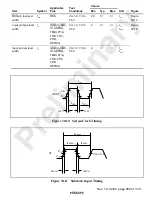

Figure 30.10 System Clock Timing

t

EXCLf

t

subcyc

t

EXCLH

t

EXCLL

t

EXCLr

V

IL

V

IH

X1

Vcc

×

0.5

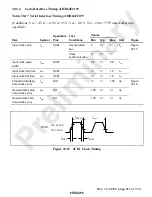

Figure 30.11 Subclock Input Timing