Rev. 1.0, 02/00, page 305 of 1141

searches. These DVCTL signals can also be used for phase controls of the capstan motor.

Also, by selecting the dividing clock as the clock source, it is possible to make a delay with the

edges of the DVCTL to provide the slow tracking mono-multi function.

15.3.4

Mode Identification

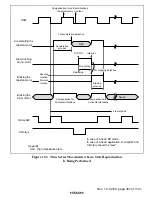

When making mode identification (2/4/6 identification) of the SP/LP/EP modes of reproducing

tapes, the TMRU-1 (CFG dividing circuit), TMRU-2 (capturing function/without reloading

function) and TMRU-3 (DVCTL dividing circuit) of timer R should be used.

Timer R will become to the aforementioned status after a reset.

Under the aforementioned status, the divided CFG should be written into the reloading register of

the TMRU-1 and divided DVCTL should be written into the reloading register of the TMRU-3.

When the TMRU-3 underflows, the counter value of the TMRU-2 is captured. Such capturing

register value represents the number of the CFG within the DVCTL cycle.

As aforementioned, the Timer R can work to count the number of the CFG corresponding to n

times of DVCTL's or to identify the mode being searched.

For register settings, see section 15.5.1, Mode Identification.

15.3.5

Reeling Controls

CFG counts can be captured by making 16-bit capturing operation combining the TMRU-1 and

TMRU-2. Choosing the IRQ3 as the capture signal and counting the CFG within the duration of

the reel pulse being input through the

,54

6

pin affect reeling controls. For register settings, see

section 15.5.2, Reeling Controls.

15.3.6

Acceleration and Braking Processes of the Capstan Motor

When making intermittent movements such as those for slow reproductions or for still

reproductions, it is necessary to conduct quick accelerations and abrupt stoppings of the capstan

motor. The acceleration and braking processes functions to check if the revolution of a capstan

motor has reached the prescribed rate when accelerated or braked. For this purpose, the TMRU-2

(reloading function) should be used.

When making accelerations:

•

Set the AC/BR bit of the TMRM1 to acceleration (set to 1). Also, use the rising edge of the

CFG as the reloading signal.

•

Set the prescribed time on the CFG frequency to determine if the acceleration has been

finished, into the reloading register.

•

The TMRU-2 will work to down-count the reloading data.

•

In case the acceleration has not been finished (in case the CFG signal is not input even when

the prescribed time has elapsed = underflowing of down-counting has occurred), such