Rev. 1.0, 02/00, page 320 of 1141

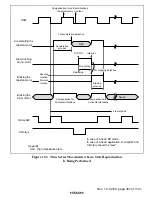

Edge detection and

capture signal

generating circuit.

BUFEA

IEDGA

FTIA

IEDGC

ICRC

ICRA

FRC

Figure 16.2 Buffer Operation (Example)

Table 16.3

Input Signal Edge Selection when Making Buffer Operation

IEDGA

IEDGC

Selection of the Input Signal Edge

0

Captures at the falling edge of the input capture input A (Initial value)

0

1

0

Captures at both rising and falling edges of the input capture input A

1

1

Captures at the rising edge of the input capture input A

Reading can be made from the ICR through the CPU at 8-bit or 16-bit.

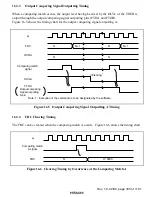

For stable input capturing operation, maintain the pulse duration of the input capture input signals

at 1.5 system clock (

φ

) or more in case of single edge capturing and at 2.5 system clock (

φ

) or

more in case of both edge capturing.

The ICR is initialized to H'0000 when reset or under the standby mode, watch mode, subsleep

mode, module stop mode or subactive mode.