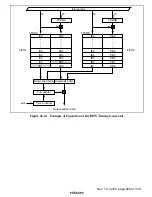

Rev. 1.0, 02/00, page 609 of 1141

Output pattern data

φ

s/4

W

W

FTPRB

FIFO2

tB0

PB9

tB5

PB4

tB4

PB3

tB3

PB2

tB2

PB1

tB1

PB0

W

W

FPDRA

Output select buffer Output data buffer

Comparator

FTPRA

FIFO1

tA0

PA9

tA5

PA4

tA4

PA3

tA3

PA2

tA2

PA1

tA1

PA0

Internal bus

FPDRB

Timer counter

Figure 26.24 Example of Operation of the HSW Timing Generator