Rev. 1.0, 02/00, page 556 of 1141

26.1.2

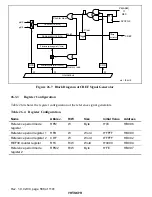

Block Diagram

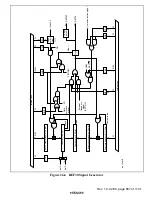

Figure 26.1 shows a block diagram of the servo circuits.

4-head

special

playback

controller

- +

SV1(P30)

EXCAP(P81)

( )

SV2(P31)

( )

EXCTL(P82)

)

+

+

+

+

+

- +

- +

-

CTL

Head

CTL Amp

CTL

Head

CFG

CAP

PWM

DRM

PWM

DFG

DPG(P87)

VIDEOFF

AUDIOFF

Vpulse

H.Amp SW(P84)

C.ROTARY(P83)

COMP(P85)

Csync

EXTTRG(P86)

OSCH

REC:ON

ADTRIG

(HSW)

Ep

PWM

Es

Es

Ep

REC

REC

PB.ASM

CTLFB

PB.CTL

PB.

ASM

(NTSC)

DVCTL

Gain control

by register

setting

REF30,REF30X,CREF,

CTLMONI,DVCFG,

DFG,DPG,DFG,etc

Internal signal

monitor controller

(PAL)

REF30X

REC-CTL

DutyI/O

(Duty deter-

minator)

(Assemble

recording)

DVCFG

DVCFG2

Gain up.

XE:ON

VD

RP0 to 7/

(P60 to 67,

P74 to 77)

Sync

separator

REC-CTL

generator

VISS

circuit

Noise

Det.

A/D

converter

Timer X1

Timer L

Timer R

AN pins

PWM

X-value

adjustment

Gain up.

RP0 to 7/

(P60 to 67,

P74 to 77)

PPG0 to 7/

(P70 to 77)

PPG0 to 7/

(P70 to 77)

REF30P(PB:30Hz,REC:1/2VD)

CREF

Res

System

clock

Additional

V pulse

generator

Head-switch

timing

generator

Drum system

reference

signal

Capstan

system

reference

signal

Phase

error

detector

Phase

error

detector

Digital

filter

Digital

filter

Digital

filter

Digital

filter

Frequency

divider

Frequency

divider

Speed

error

detector

Speed

error

detector

Figure 26.1 Block Diagram of Servo Circuits