Rev. 1.0, 02/00, page 693 of 1141

REC-CTL Duty Data Register 2 (RCDR2)

1

1

1

1

13

14

15

1

0

3

2

5

4

7

6

9

8

11

10

CMT21

W

12

—

—

—

—

—

—

—

—

0

CMT20

W

0

CMT23

W

0

CMT22

W

0

CMT25

W

0

CMT24

W

0

CMT27

W

0

CMT26

W

0

CMT29

W

0

CMT28

W

0

CMT2B

W

0

CMT2A

W

0

Bit :

Initial value :

R/W :

RCDR2 is a 12-bit write-only register that sets 1 pulse (short) falling timing of REC-CTL at

recording and rewriting, and detects long/short pulses at detecting.

Only a word access is valid. If a byte access is attempted, correct operation is not guaranteed. If a

read is attempted, an undetermined value is read out. Bits 15 to 12 are reserved and are not

affected by write access.

RCDR2 is initialized to H'F000 by a reset, and in standby mode, module stop mode, and CTL stop

mode.

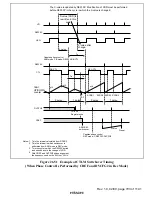

At recording, the value to set in RCDR2 can be calculated from the transition timing T2 and the

servo clock frequency

φ

s by the equation given below, and the set value should be 25% of the duty

obtained by the equation. See figure 26.60, REC-CTL Signal Generation Timing.

RCDR2 = T2

×

φ

s/64

φ

s is the servo clock frequency (= f

OSC

/2) in Hz, and T2 is the set timing (s).

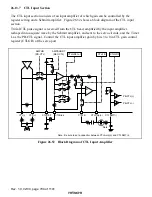

At bit pattern detection, set the 1 pulse long/short threshold value at FWD. See figure 26.56, Duty

Discriminator.

RCDR2 = T2'

×

φ

s/64

φ

s is the servo clock frequency (= f

OSC

/2) in Hz, and T2' is the 1 pulse long/short threshold value at

FWD (s).