Rev. 1.0, 02/00, page 619 of 1141

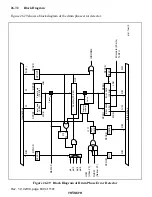

W

W

R

UDF

OVF

Lock 2 up

Clear

Latch

Preset

DFVCR

DFRLOR

DFVCR

DFPR

DFVCR

DFVCR

DFVCR

DFUCR

FGCR

DFER

DFRVCR

Error data

(16 bits)

To DFU

ADDFGN

NCDFG

DFRUDR

Internal bus

W

R/W

Internal bus

R/W

W

R/W

R/W

R/W

R/W

(R)/W

Lock 1 up

S

R

F/F

Q

S

R

F/F

DFRCS1,0

DF-R/UNR

Lock counter

(2 bits)

Q

S

R

F/F

Q

Lock range

detector

Lock range data 1 (16bit)

DPCNT

Error data

limiter

control circuit

DFEFON

DFESS

DRF

Edge

detector

↑

,

↓

Error data (16 bits)

Counter (16 bits)

DFOVF

IRRDRM2

IRRDRM1

To DROCKON

DFU

Preset data

(16 bits)

Lock range data 2

(16 bits)

DFCS1,0

φ

s

φ

s/2

φ

s/4

φ

s/8

Figure 26.27 Block Diagram of the Drum Speed Error Detector