Rev. 1.0, 02/00, page 786 of 1141

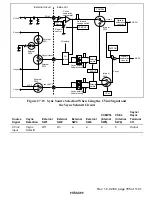

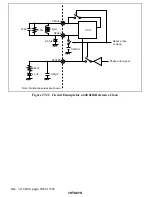

(b) Using the Csync Schmitt Circuit

The Hsync component is processed in the same way as described in (a), but the Vsync

component is processed differently; the Csync/Hsync terminal is left open and the

separated Vsync component is input through the Csync Schmitt circuit to the digital V

separation counter. Figure 27.16 shows this method.

CVin2

Csync

a

1

1

0

0

b

a

b

Hsync

Vsync

VLPF

Vsync/VLPF

Csync/Hsync

Hsync

Vsync

External

SW3

Internal

SW5

Internal

SW6

External

SW2

External

SW1

Reference

voltage switch

Register

control

I/O switch

I/O

switch

Polarity

switch

Polarity

switch

Digital H

separation

counter

Digital V

separation

counter

DLPFON

Csync polarity

Schmitt circuit

Vsync polarity

Schmitt circuit

External circuit

Inside LSI

Csync

separation

comparator

External

SW4

CVin2

–

+

CCMPSL

CCMPV0, 1

SYNCT

VSEL

SEPV

SEPH

Sync tip

clamp

Figure 27.16 Sync Source Selection When Using the CVin2 Signal and

the Csync Schmitt Circuit

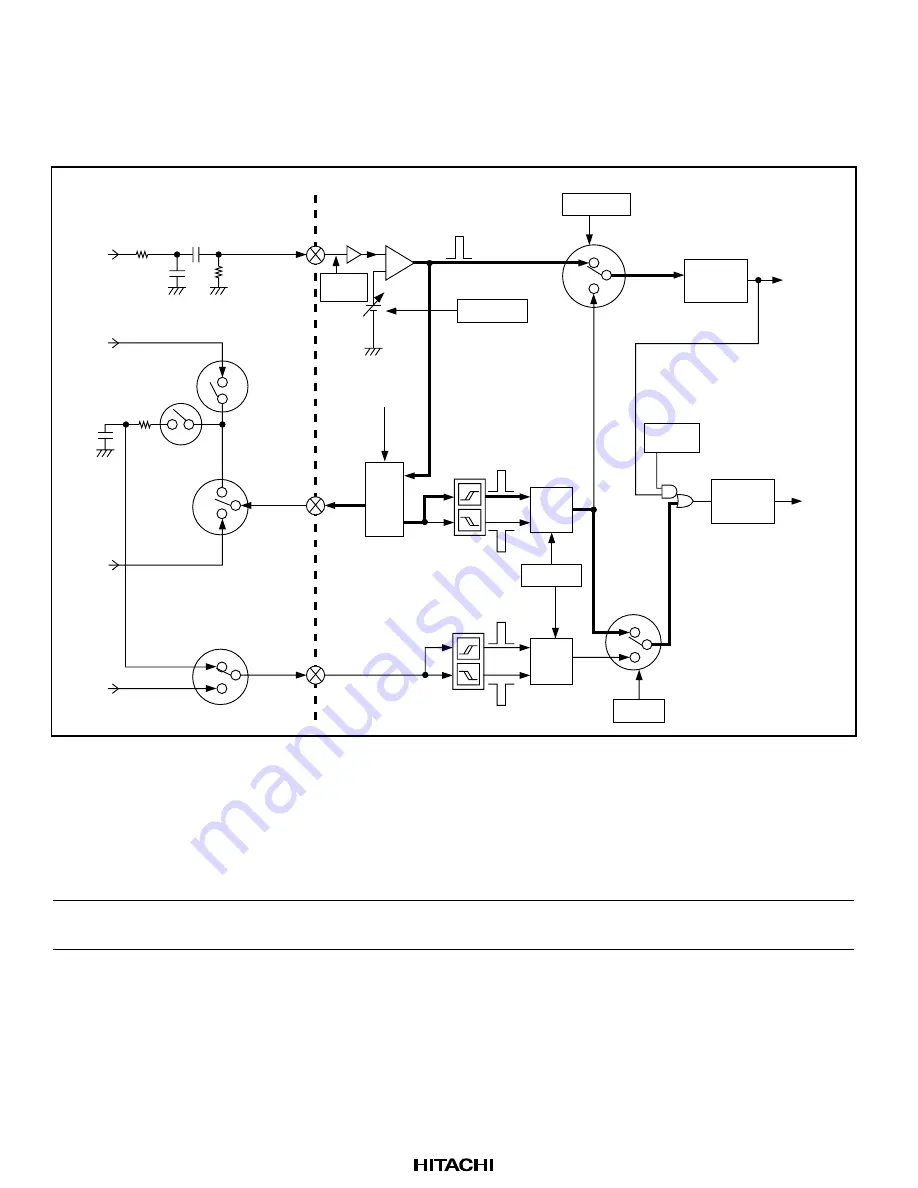

Source

Signal

Vsync

Detection

External

SW1

External

SW2

External

SW3

External

SW4

CCMPSL

(Internal

SW5)

VSEL

(Internal

SW6)

Csync/

Hsync

Terminal

I/O

CVin2

input

Csync

Schmitt

Off

Off

Open

Fixed to

0 or 1

0

1

Output