Rev. 1.0, 02/00, page xvi of 19

26.15.6

Noise Detection ................................................................................................ 744

26.15.7

Activation of the Sync Signal Detector ............................................................ 747

26.16 Servo Interrupt .................................................................................................................. 748

26.16.1

Overview .......................................................................................................... 748

26.16.2

Register Configuration...................................................................................... 748

26.16.3

Register Description ......................................................................................... 748

Section 27 Sync Separator for OSD and Data Slicer

................................................ 757

27.1

Overview........................................................................................................................... 757

27.1.1

Features............................................................................................................. 758

27.1.2

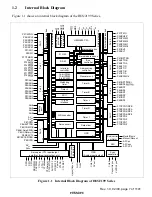

Block Diagram.................................................................................................. 758

27.1.3

Pin Configuration ............................................................................................. 760

27.1.4

Register Configuration...................................................................................... 760

27.2

Register Description.......................................................................................................... 761

27.2.1

Sync Separation Input Mode Register (SEPIMR) ............................................ 761

27.2.2

Sync Separation Control Register (SEPCR) ..................................................... 765

27.2.3

Sync Separation AFC Control Register (SEPACR) ......................................... 768

27.2.4

Horizontal Sync Signal Threshold Register (HVTHR) .................................... 770

27.2.5

Vertical Sync Signal Threshold Register (VVTHR)......................................... 773

27.2.6

Field Detection Window Register (FWIDR) .................................................... 775

27.2.7

H Complement and Mask Timing Register (HCMMR) ................................... 777

27.2.8

Noise Detection Counter (NDETC).................................................................. 779

27.2.9

Noise Detection Level Register (NDETR) ....................................................... 780

27.2.10

Data Slicer Detection Window Register (DDETWR) ...................................... 781

27.2.11

Internal Sync Frequency Register (INFRQR)................................................... 783

27.3

Operation .......................................................................................................................... 784

27.3.1

Selecting Source Signals for Sync Separation .................................................. 784

27.3.2

Vsync Separation .............................................................................................. 790

27.3.3

Hsync Separation .............................................................................................. 791

27.3.4

Field Detection ................................................................................................. 792

27.3.5

Noise Detection ................................................................................................ 792

27.3.6

Automatic Frequency Controller (AFC) ........................................................... 793

27.3.7

Module Stop Control Register (MSTPCR)....................................................... 797

Section 28 Data Slicer

........................................................................................................ 799

28.1

Overview........................................................................................................................... 799

28.1.1

Features............................................................................................................. 799

28.1.2

Block Diagram.................................................................................................. 800

28.1.3

Pin Configuration ............................................................................................. 801

28.1.4

Register Configuration...................................................................................... 802

28.1.5

Data Slicer Use Conditions............................................................................... 802

28.2

Register Description.......................................................................................................... 803

28.2.1

Slice Even- (Odd-) Field Mode Register (SEVFD, SODFD) ........................... 803