Rev. 1.0, 02/00, page 311 of 1141

Settings

•

Setting the timer R mode register 2 (TMRM2)

PS31 and PS30 (bits 4 and 3) = Other than (0, 0): The dividing clock is to be used as the

clock source for the TMRU-3.

CP/SLM bit (bit 2) = 1: The slow tracking delay signal is to work to issue the TMRI3

interrupt request.

•

Setting the timer R load register 3 (TMRL3)

Set the slow tracking delay value. When the delay count is n, the set value should be

(n - 1).

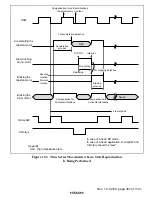

Regarding the delaying duration, see figure 15.2.

15.5.4

Acceleration and Braking Processes of the Capstan Motor

When making intermittent movements such as those for slow reproductions or for still

reproductions, it is necessary to conduct quick accelerations and abrupt stoppings of the capstan

motor. The acceleration and braking processes will function to check if the revolution of a capstan

motor has reached the prescribed rate when accelerated or braked. For this purpose, the TMRU-2

(reloading function) should be used.

The acceleration and braking processes should be employed when making special reproductions,

in combination with the slow tracking mono-multi function.

Settings for the acceleration process

•

Setting the timer R mode register 1 (TMRM1)

AC/BR bit (bit 6) = 1: Acceleration process

RLD bit (bit 5) = 1: The TMRU-2 is to be used as the reload timer.

RLCK bit (bit 4) = 0: The TMRU-2 is to reload at the rising edge of the CFG.

PS21 and PS20 (bits 3 and 2) = Other than (0, 0): The dividing clock is to be used as the

clock source for the TMRU-2.

•

Setting the timer R load register 2 (TMRL2)

Set the count reading for the duration until the acceleration process finishes. When the

count is n, the set value should be (n

−

1).

Regarding the duration until the acceleration process finishes, see figure 15.2.

Settings for the braking process

•

Setting the timer R mode register 1 (TMRM1)

AC/BR bit (bit 6) = 0: Braking process

RLD bit (bit 5) = 1: The TMRU-2 is to be used as the reload timer.

RLCK bit (bit 4) = 0: The TMRU-2 is to reload at the rising edge of the CFG.