Rev. 1.0, 02/00, page 299 of 1141

Bit 2

TMRI1 Interrupt Requesting Flag (TMRI1): This is the TMRI1 interrupt requesting

flag.

It indicates occurrences of the TMRU-1 underflow signals.

Bit 2

TMRI1

Description

0

[Clearing conditions]

(Initial value)

When 0 is written after reading 1.

1

[Setting conditions]

When the TMRU-1 underflows.

Bits 1 and 0

Reserved: These bits cannot be modified and are always read as 1.

15.2.4

Timer R Capture Register 1 (TMRCP1)

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

R

TMRC17

R

TMRC16

R

TMRC15

R

TMRC14

R

TMRC13

R

TMRC12

R

TMRC11

R

TMRC10

Bit :

Initial value :

R/W :

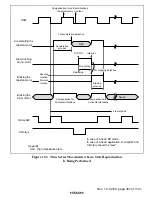

The timer R capture register 1 (TMRCP1) works to store the captured data of the TMRU-1.

During the course of the capturing operation, the TMRU-1 counter readings are captured by the

TMRCP1 at the CFG edge or the IRQ3 edge. The capturing operation of the TMRU-1 is

performed using 16 bits, in combination with the capturing operation of the TMRU-2.

The TMRCP1 is an 8-bit read only register. When reset, the TMRCS is initialized to H'FF.

Notes: 1. When the TMRCP1 is readout while the capture signal is being received, the reading

data become unstable. Pay attention to the timing for reading out.

2. When a shift to the low power consumption mode is made while the capturing

operating is in progress, the counter reading becomes unstable. After returning to the

active mode, always write H'FF into the TMRL1 to initialize the counter.