Rev. 1.0, 02/00, page 722 of 1141

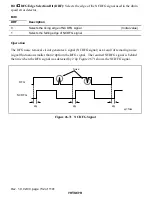

26.14.3

CFG Frequency Divider

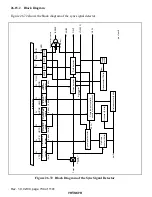

Block Diagram: Figure 26.65 shows a block diagram of the 7-bit CFG frequency divider and its

mask timer.

W

R/W

W

W

W

W

W

R

W

Internal bus

CMN

CRF

UDF

UDF

UDF

CFG

DVCFG

DVCFG2

↑

,

↑↓

MCGin

Internal bus

CPS1,

CPS0

CTMR(6 bits)

CDIVR2(7 bits)

DVTRG

PB(ASM)

→

REC

φ

s = fosc/2

φ

s/1024

φ

s/512

φ

s/256

φ

s/128

Down counter (6 bits)

CDIVR(7 bits)

CMK

S

R

Edge

select

CDVC

CDVC

CDVC

CDVC

CDVC

Down counter (7 bits)

Down counter (7 bits)

Figure 26.65 CFG Frequency Divider