Rev. 1.0, 02/00, page 933 of 1141

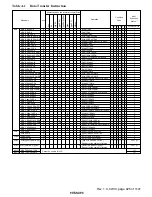

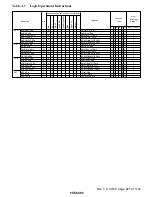

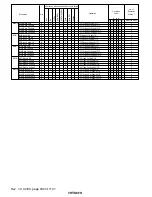

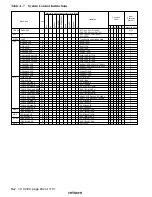

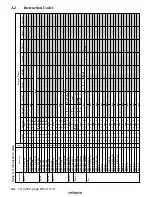

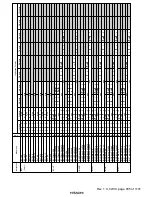

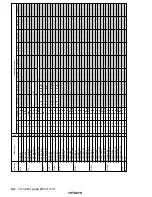

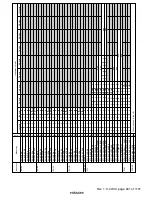

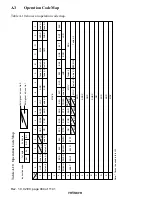

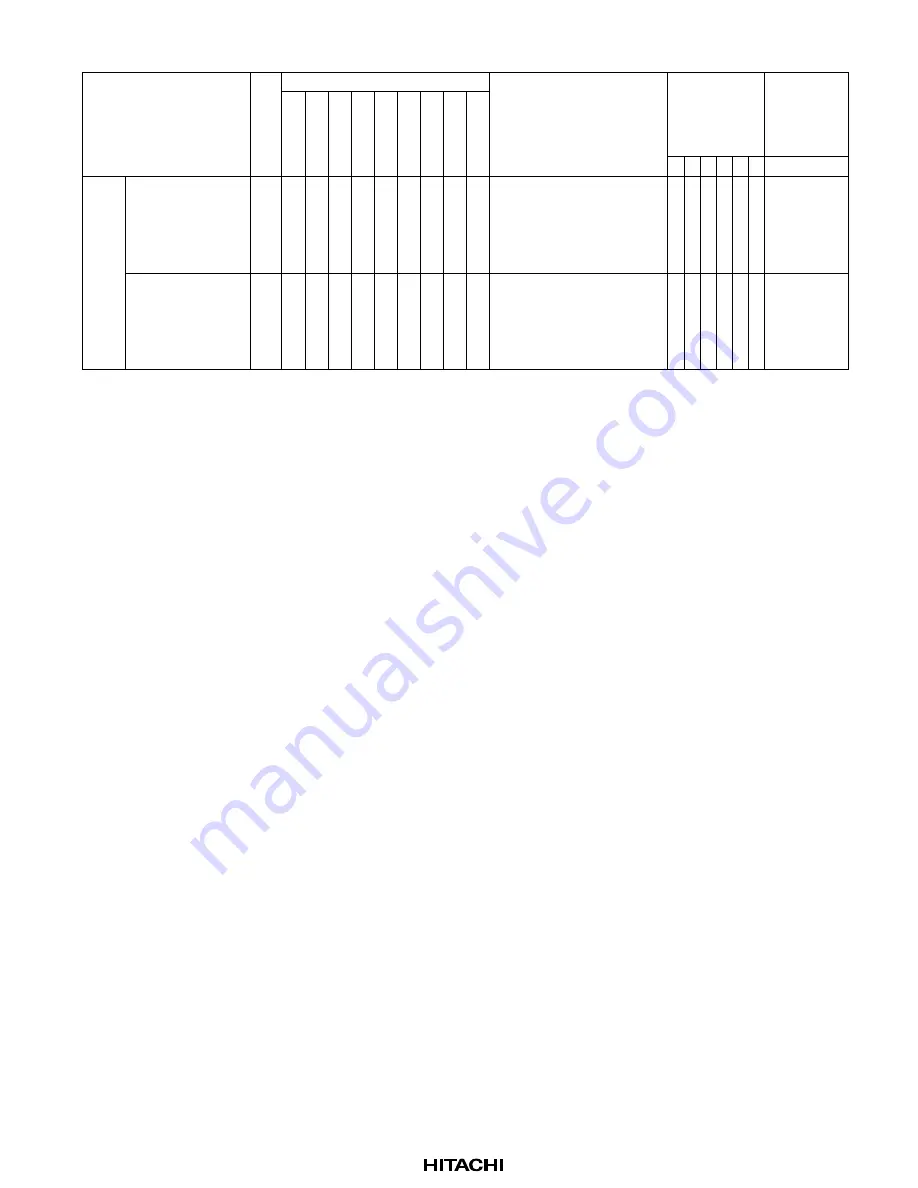

Table A.8

Block Transfer Instructions

EEPMOV.B

EEPMOV.W

—

—

EEPMOV

Mnemonic

Size

#xx

Rn

@ERn

@(d,ERn)

@-ERn/@ERn+

@aa

@(d,PC)

@@aa

—

Operation

I

H N Z V C

Advanced Mode

4

4

4+2n *

2

4+2n *

2

—

—

—

—

—

—

—

—

—

—

—

—

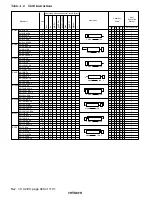

Condition

Code

if R4L

≠

0

Repeat @ER5

→

@ER6

ER5+1

→

ER5

ER6+1

→

ER6

R4L-1

→

R4L

Until R4L=0

else next;

if R4

≠

0

Repeat @ER5

→

@ER6

ER5+1

→

ER5

ER6+1

→

ER6

R4-1

→

R4

Until R4=0

else next;

Addressing Mode and Instruction Length (Bytes)

No of

Execution

States

*1

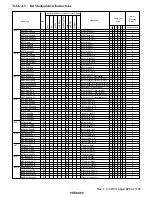

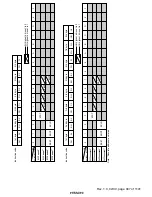

Notes: 1. The values indicated in the column of number of execution states apply when

instruction code and operand exist in the on-chip memory.

2. n is the initial setting value of R4L or R4.

[1] 7 states when the number of return/retract registers is 2, 9 states when the number of

registers is 3, and 11 states when the number of registers is 4.

[2] Cannot be used in this LSI.

[3] Set to 1 when a carry or borrow occurs at bit 11, otherwise cleared to 0.

[4] Set to 1 when a carry or borrow occurs at bit 27, otherwise cleared to 0.

[5] Retains the value before computation when the computation result is 0, otherwise

cleared to 0.

[6] Set to 1 when the divisor is negative, otherwise cleared to 0.

[7] Set to 1 when the divisor is 0, otherwise cleared to 0.

[8] Set to 1 when the quotient is negative, otherwise cleared to 0.

[9] 1 is added to the number of execution states when EXR is valid.