Rev. 1.0, 02/00, page 395 of 1141

21.4.2

Prescalar W (PSW)

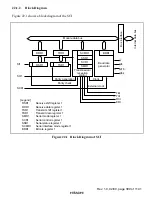

PSW is a counter that uses the subclock as an input clock. The PSW also generates the input

clock of the timer A. In this case, the timer A functions as a clock time base.

When reset, the PSW is initialized to H'00, and starts increment after reset has been released.

Even if the mode has been shifted to the standby mode *, watch mode *, subactive mode *, and

subsleep mode *, the PSW continues the operation as long as the clocks are supplied by the X1

and X2 pins.

The PSW can also be initialized to H'00 by setting the TMA3 and TMA2 bits of the timer mode

register A (TMA) to 11.

Note: *

When the timer A is in module stop mode, the operation is stopped.

Figure 21.2 shows the supply of the clocks to the peripheral function by the PSS and PSW.

φ

/131072 to

φ

/2

φ

Timer

SCI

OSC1

fosc

OSC2

φ

w/128

φ

w/4

φ

w

Timer A

Prescalar S

X1

(fx)

X2

CPU

ROM

RAM

TMOW pin

Peripheral register

I/O port

Intermediate

speed clock

frequency divider

Prescalar W

System clock

selection

Subclock

frequency

dividers

(1/2, 1/4, and 1/8)

Subclock

oscillator

System

clock

oscillator

System

clock

duty

correction

circuit

Figure 21.2 Clock Supply

21.4.3

Stable Oscillation Wait Time Count

For the count of the stable oscillation stable wait time during the return from the low power

consumption mode excluding the sleep mode, see section 4, Power-Down State.