Rev. 1.0, 02/00, page 1020 of 1141

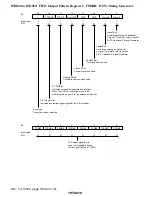

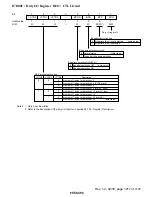

H'D098: DVCTL Control Register CTVC: Frequency Divider

0

*

1

*

R

2

*

R

3

4

5

6

7

R

CFG

HSW

0

W

0

W

CEX

CEG

CTL

1

1

1

DVCTL signal generation select bit

0 Generated by PB-CTL signal (Initial value)

1 Generated by external input signal

External sync signal edge select bit

0 Rising edge

(Initial value)

1 Falling edge

CFG flag

0 CFG level is low

(Initial value)

1 CFG level is high

HSW flag

0 HSW level is low

(Initial value)

1 HSW level is high

CTL flag

0 REC or PB-CTL level is low

(Initial value)

1 REC or PB-CTL level is high

—

—

—

—

—

—

Bit

Initial value

R/W

:

:

:

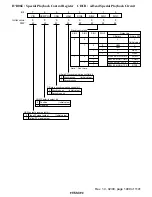

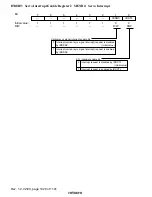

H'D099: CTL Frequency Division Register CTLR: Frequency Divider

0

0

1

0

W

2

0

W

3

0

4

0

W

0

W

5

6

0

7

CTL4

CTL3

CTL2

CTL1

CTL0

0

W

CTL7

W

W

W

CTL6

CTL5

Bit

Initial value

R/W

:

:

: