Rev. 1.0, 02/00, page 518 of 1141

AHR can be read by the CPU at any time, but the AHR value during A/D conversion is not fixed.

The upper bytes can always be read directly, but the data in the lower bytes is transferred via a

temporary register (TEMP). For details, see section 24.3, Interface to Bus Master.

AHR is a 16-bit read-only register which is initialized to H'0000 at a reset, and in module stop

mode, standby mode, watch mode, subactive mode and subsleep mode.

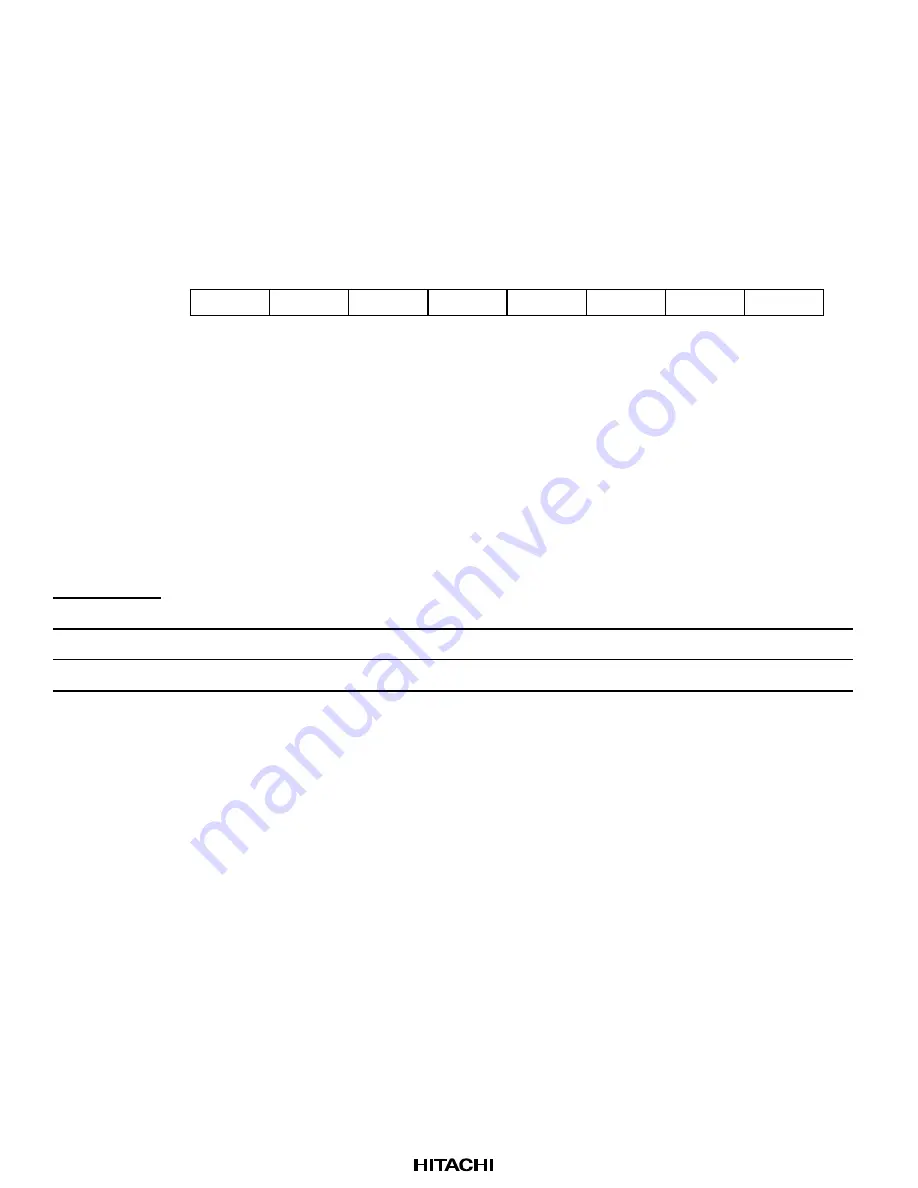

24.2.3

A/D Control Register (ADCR)

0

0

1

0

R/W

2

0

R/W

3

0

4

0

R/W

5

0

6

—

—

1

7

R/W

R/W

R/W

HCH1

0

R/W

CK

HCH0

SCH3

SCH2

SCH1

SCH0

Bit :

Initial value :

R/W :

ADCR is a register that sets A/D conversion speed and selects analog input channel. When

executing ADCR setting, make sure that the SST and HST flags in ADCSR is set to 0.

ADCR is an 8-bit readable/writable register that is initialized to H'40 by a reset, and in module

stop mode, standby mode, watch mode, subactive mode and subsleep mode.

Bit 7

Clock Select (CK): Sets A/D conversion speed.

Bit 7

CK

Description

0

Conversion frequency is 266 states

(Initial value)

1

Conversion frequency is 134 states

Note:

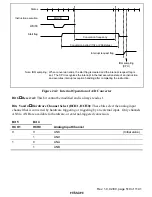

A/D conversion starts when 1 is written in SST, or when HST is set to 1. The conversion

period is the time from when this start flag is set until the flag is cleared at the end of

conversion. Actual sample-and-hold takes place (repeatedly) during the conversion

frequency shown in figure 24.2.