Rev. 1.0, 02/00, page 590 of 1141

R

W

W

R/W

R/W

W

R/W

R/W

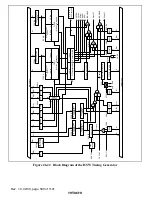

STRIG

IRRHSW2

ISEL2

AudioFF

VideoFF

HSW

NHSW

Mlevel

Vpulse

ADTRG

IRRHSW1

R

VD

PB

W

R/W

R/W

Cleared

Cleared

CLK

W

R

↑

,

↓

NCDFG

FRCOVF

DPG

↑

CKSL

VFF/NFF

Internal bus

W

FPDRA

FPDRB

FTPRA

FTPRB

W

ISEL1

OFG

FIFO output pattern

register 1

FIFO output pattern

register 2

SOFG

LOP

R/W

R/W

R

R

WW

CLRA,B

OVWA,B

EMPA,B

FLA,B

R/W

R/W

HSM2

HSM1

HSLP

EDG

HSW loop stage

number setting

register

Internal bus

FGR20FF

FRT

CCLR

Edge

detector

Control

circuit

FIFO 1

(31 bits

×

10 stages)

15 bits

P77 to 70

(PPG output)

FIFO timing pattern

register 1

FIFO timing pattern

register 2

16 bits

FIFO2

(31 bits

×

10 stages)

15 bits

16 bits

FIFO output selector & output buffer

15 bits

16 bits

DFCRB

DFCRA

DFCRA

HSM2

HSM2

Capture

HSM2

DFCRA

DFCRA

DFG reference

register 1

Comparator

(5 bits)

Comparator

(5 bits)

DFG reference

register 2

DFCTR

5-bit counter

Compare circuit (16 bits)

FTCTR (16 bits)

16-bit timer counter

φ

s/4

φ

s/8

Figure 26.22 Block Diagram of the HSW Timing Generator