Rev. 1.0, 02/00, page 147 of 1141

7.5

Programming/Erasing Flash Memory

In the on-board programming modes, flash memory programming and erasing is performed by

software, using the CPU. There are four flash memory operating modes: program mode, erase

mode, program-verify mode, and erase-verify mode. With addresses H'00000 to H'3FFFF,

transitions to these modes can be made by setting the PSU1, ESU1, P1, E1, PV1 and EV1 bits in

FLMCR1. With addresses H'40000 to H'47FFF, transitions to these modes can be made by setting

the PSU2, ESU2, P2, E2, PV2, and EV2 bits in the FLMCR2.

The flash memory cannot be read while being programmed or erased. Therefore, the program that

controls flash memory programming/erasing (the programming control program) should be

located and executed in on-chip RAM or external memory.

Notes: 1. Operation is not guaranteed if setting/resetting of the SWE1, ESU1, PSU1, EV1, PV1,

E1, and P1 bits in FLMCR1, and the SWE2, ESU2, PSU2, EV2, PV2, E2, and P2 in

FLMCR2, is executed by a program in flash memory.

2. When programming or erasing, set FWE to 1 (programming/erasing will not be

executed if FWE = 0).

3. Perform programming in the erased state. Do not perform additional programming on

previously programmed addresses.

4. Do not write to addresses H'00000 to H'3FFFF and H'40000 to H'47FFF at the same

time. Otherwise operation cannot be guaranteed.

5. Do not operate the OSD when writing or erasing addresses H'40000 to H'47FFF. Do

not set the OSROME in STCR to 1 before manipulating the flash control register.

7.5.1

Program Mode (n=1 when the target address range is H'00000 to H'3FFFF and

n=2 when the target address range is H'40000 to H'47FFF)

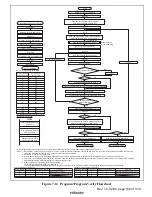

Follow the procedure shown in the program/program-verify flowchart in figure 7.12 to write data

or programs to flash memory. Performing program operations according to this flowchart will

enable data or programs to be written to flash memory without subjecting the device to voltage

stress or sacrificing program data reliability. Programming should be carried out 128 bytes at a

time.

Following the elapse of 1.0

µ

s or more after the SWEn bit is set to 1 in flash memory control

register n (FLMCRn), 128-byte program data is stored in the program data area and reprogram

data area, and the 128-byte data in the reprogram data area written consecutively to the write

addresses. The lower 8 bits of the start address written to must be H'00, or H'80. One hundred

and twenty-eight consecutive byte data transfers are performed. The program address and

program data are latched in the flash memory. A 128-byte data transfer must be performed even if

writing fewer than 128 bytes; in this case, H'FF data must be written to the extra addresses.

Next, the watchdog timer is set to prevent overprogramming in the event of program runaway, etc.

Set 6.6 ms as the WDT overflow period. After this, preparation for program mode (program

setup) is carried out by setting the PSUn bit in FLMCRn, and after the elapse of 50

µ

s or more, the

operating mode is switched to program mode by setting the Pn bit in FLMCRn. The time during