Rev. 1.0, 02/00, page 1110 of 1141

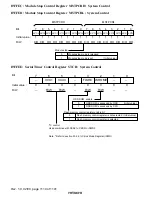

H'FFEC: Module Stop Control Register MSTPCRH: System Control

H'FFED: Module Stop Control Register MSTPCRL: System Control

7

1

MSTP15

R/W

MSTPCRH

6

1

MSTP14

R/W

5

1

MSTP13

R/W

4

1

MSTP12

R/W

3

1

MSTP11

R/W

2

1

MSTP10

R/W

1

1

MSTP9

R/W

0

1

MSTP8

R/W

7

1

MSTP7

R/W

6

1

MSTP6

R/W

5

1

MSTP5

R/W

4

1

MSTP4

R/W

3

1

MSTP3

R/W

2

1

MSTP2

R/W

1

1

MSTP1

R/W

0

1

MSTP0

R/W

MSTPCRL

Module stop

Module stop mode is released

Module stop mode is set

(Initial value)

0

1

Bit

Initial value

R/W

:

:

:

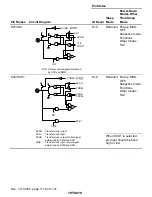

H'FFEE: Serial Timer Control Register STCR: System Control

7

—

0

—

6

IICX1

0

R/W

5

IICX0

0

R/W

4

—

0

—

3

FLSHE

0

R/W

2

OSROME

0

R/W

1

—

0

—

0

—

0

—

Flash memory control register enable bit

OSD ROM enable

I

2

C control

Used combined with CKS2 to CKS0 in ICMR0

Note: * Refer to section 23.2.4, I

2

C Bus Mode Register (ICMR)

OSD ROM is accessed by OSD

(Initial value)

OSD ROM is accessed by CPU

0

1

Flash memory control register is not selected (Initial value)

Flash memory control register is selected

0

1

Bit

Initial value

R/W

:

:

: