Rev. 1.0, 02/00, page 514 of 1141

24.1.2

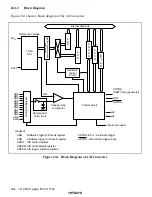

Block Diagram

Figure 24.1 shows a block diagram of the A/D converter.

φ

/2

φ

/4

ADTRG

Interrupt request

AN0

Vref

AV

CC

AV

SS

Reference Voltage

Sample-and-

hold circuit

Chopper type

comparator

AN1

AN2

AN3

AN4

AN5

AN6

AN7

AN8

AN9

ANA

ANB

DFG

ADTRG

(HSW timing generator)

Internal data bus

[Legend]

ADR

AHR

: Software trigger A/D result register

: Hardware trigger A/D result register

ADTRG, DFG

ADTRG

: Hardware trigger

: A/D external trigger input

ADCR

ADCSR

: A/D control register

: A/D control/status register

ADTSR: A/D trigger selection register

-

+

10-bit

D/A

Hardware

control

circuit

Control circuit

Analog multiplexer

Successive

approximation register

A

D

R

A

H

R

A

D

C

S

R

A

D

C

R

A

D

T

S

R

Figure 24.1 Block Diagram of A/D Converter