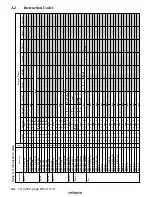

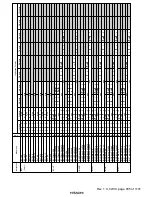

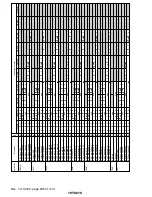

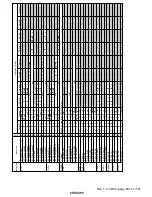

Rev. 1.0, 02/00, page 923 of 1141

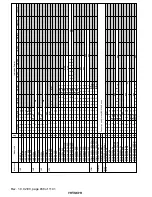

Appendix A Instruction Set

A.1

Instructions

Operation Notation

Rd

General register (destination)

*

1

Rs

General register (source)

*

1

Rn

General register

*

1

ERn

General register (32-bit register)

MAC

Multiplication-Addition register (32-bit register)

*

2

(EAd)

Destination operand

(EAs)

Source operand

EXR

Extend register

CCR

Condition code register

N

N (negative flag) in CCR

Z

Z (zero) flag in CCR

V

V (overflow) flag in CCR

C

C (carry) flag in CCR

PC

Program counter

SP

Stack pointer

#IMM

Immediate data

disp

Displacement

+

Addition

−

Subtraction

×

Multiplication

÷

Division

∧

Logical AND

∨

Logical OR

⊕

Exclusive logical OR

→

Move from the left to the right

∼

Logical complement

( ) <>

Contents of operand

:8/:16/:24/:32

8/16/24/32 bit length

Notes: 1. General register is 8-bit (R0H to R7H, R0L to R7L), 16-bit (R0 to R7) or 32-bit (ER0 to

ER7).

2. MAC register cannot be used in this LSI.