Rev. 1.0, 02/00, page 1086 of 1141

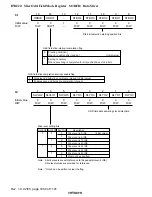

H'D244: Vertical Sync Signal Threshold Register VVTHR: Sync Separator

0

1

2

VVTH2

3

VVTH3

0

4

VVTH4

W

W

W

W

W

W

W

5

VVTH5

6

VVTH6

7

VVTH7

VVTH1

0

W

VVTH0

0

0

0

0

0

0

:

:

:

Vertical sync signal threshold

Note: Refer to section 27.2.5, Vertical Sync Signal Threshold Register (VVTHR)

Bit

Initial value

R/W

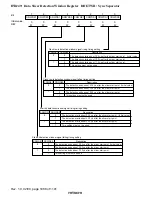

H'D245: Field Detection Window Register FWIDR: Sync Separator

0

1

2

FWID2

3

FWID3

0

4

—

—

W

W

W

5

—

—

6

—

—

7

—

—

FWID1

0

W

FWID0

1

1

1

1

0

0

:

:

:

Field detection window timing

Note: Refer to section 27.2.6, Field Detection Window Register (FWIDR)

Bit

Initial value

R/W

H'D246: H Complement and Mask Timing Register HCMMR: Sync Separator

1

0

3

2

5

4

7

0

W

6

0

W

9

0

W

8

0

W

11

0

W

10

0

W

0

W

0

W

0

W

HC8

HC7

HC6

HC5

HC4

HC3

HC2

HC1

HC0

HM6

W

HM5

W

HM4

W

HM3

W

HM2

W

HM1

W

HM0

0

W

12

13

14

15

0

0

0

0

0

0

:

:

:

HHK clearing timing

Complementary pulse

generation timing

Note: Refer to section 27.2.7, H Complement and Mask Timing Register (HCMMR)

Bit

Initial value

R/W