Rev. 1.0, 02/00, page 589 of 1141

26.4

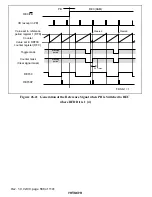

HSW (Head-switch) Timing Generator

26.4.1

Overview

The HSW timing generator consists of a 5-bit DFG counter, a 16-bit timer counter, a matching

circuit, and two 31-bit 10-stage FIFOs.

The 5-bit counter counts the DFG pulses following a DPG pulse. Each of them determines the

timing to reset the 16-bit timer counter for each field. The 16-bit timer counter is a timer clocked

by a

φ

s/4 clock source, and can be used as a programmable pattern generator (PPG) as well as a

free-running counter (FRC). If used as a free-running counter, it is cleared by overflow of the 19-

bit FRC. Accordingly, two FRCs operate synchronously. The matching circuit compares the

timing data in the most significant 16 bits of FIFO with the 16-bit timer counter, and controls the

output of the pattern data set in the least significant 15 bits of FIFO.

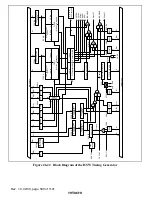

26.4.2

Block Diagram

Figure 26.22 shows a block diagram of the HSW timing generator.